# Materials for Information Technology

Devices, Interconnects and Packaging

#### Series Editor

Professor Brian Derby, Professor of Materials Science Manchester Materials Science Centre, Grosvenor Street, Manchester, M1 7HS, UK

#### Other titles published in this series:

*Fusion Bonding of Polymer Composites* C. Ageorges and L. Ye

*Composite Materials* D.D.L. Chung

*Titanium* G. Lütjering and J.C. Williams

*Corrosion of Metals* H. Kaesche

*Corrosion and Protection* E. Bardal

Intelligent Macromolecules for Smart Devices L. Dai

*Microstructure of Steels and Cast Irons* M. Durand-Charre

Phase Diagrams and Heterogeneous Equilibria B. Predel, M. Hoch and M. Pool

Computational Mechanics of Composite Materials M. Kamiński

Gallium Nitride Processing for Electronics, Sensors and Spintronics S.J. Pearton, C.R. Abernathy and F. Ren Publication due September 2005

*Thermoelectricity* J.P. Heremans, G. Chen and M.S. Dresselhaus Publication due May 2006

Computer Modelling of Sintering at Different Length Scales J. Pan Publication due June 2006

Computational Quantum Mechanics for Materials Engineers L. Vitos Publication due June 2006

*Fuel Cell Technology* N. Sammes Publication due December 2005

Shape Memory Alloy Thin Films A. Ishida and S. Miyazaki Publication due March 2007 Ehrenfried Zschech, Caroline Whelan and Thomas Mikolajick (Eds.)

# Materials for Information Technology

**Devices, Interconnects and Packaging**

With 338 Figures

Ehrenfried Zschech, Dr. rer. nat. Materials Analysis Department, AMD Saxony Limited Liability Company & Co. KG, Wilschdorfer Landstraße 101, D-01109 Dresden, Germany

Caroline Whelan, Ph.D. IMEC, Kapeldreef 75, B-3001 Leuven, Belgium

Thomas Mikolajick, Dr.-Ing.

Flash Technology Predevelopment, Infineon Technologies SC300, Königsbrücker Straße 180, D-01099 Dresden, Germany

British Library Cataloguing in Publication Data

Euromat 2003 (2003 : Lausanne, Switzerland)

Materials for information technology. - (Engineering materials and processes)

1. Microelectronics - Materials - Congresses 2. Information technology - Congresses

I. Title II. Zschech, Ehrenfried III. Whelan, Caroline IV. Mikolajick, Thomas 621.3'815

ISBN-10: 1852339411

Library of Congress Control Number: 2005924304

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licences issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

Engineering Materials and Processes ISSN 1619-0181 ISBN-10: 1-85233-941-1 ISBN-13: 978-1-85233-941-8 Springer Science+Business Media springeronline.com

© Springer-Verlag London Limited 2005

The use of registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Typesetting: Electronic text files prepared by authors Production and cover design: LE-T<sub>E</sub>X Jelonek, Schmidt & Vöckler GbR, Leipzig, Germany Printed in Germany 69/3141-543210 Printed on acid-free paper SPIN 11305507

# Foreword

Euromat is the biennial meeting of the Federation of European Materials Societies (FEMS) constituted by its 24 member societies in Europe. The 2003 meeting took place in Lausanne, Switzerland, and was organised by the French, German and Swiss member societies:

- Société Française de Métallurgie et de Matériaux (SF2M)

- Deutsche Gesellschaft für Materialkunde (DGM)

- Schweizerischer Verband für die Materialtechnik (SVMT)

The scientific programme of the EUROMAT 2003 congress was divided into 15 topics that in turn were substructured into 47 symposia. The present volume of the Euromat Publication series refers to selected papers of the Topic A:

Materials for Information Technology

Peter Paul Schepp Conference Organiser of EUROMAT 2003

#### Preface

Information technology (IT) is driving the need for research, development and introduction of new materials and concepts for applications requiring significantly increased electrical and optical functionality. In particular, microelectronic products must be improved continuously to meet performance demands while maintaining acceptable levels of reliability. For the semiconductor industry, the challenges to process technology and advanced materials are outlined in the International Technology Roadmap for Semiconductors (ITRS). Microelectronic and, in the longer term, nanoelectronic products of future technology generations rely on advanced materials for the so-called front-end-of-line and back-end-of-line processes on the waferlevel (die level) as well as for assembly and packaging. More than ever before, the dramatic productivity enhancement of the IT era will only be possible using advanced materials.

Transistor and interconnect scaling has brought microelectronics a long way. However, the traditional down-scaling of device and interconnect structures is currently leading to performance limitations that have to be overcome by new device architectures and advanced materials. Microprocessor applications are pushing material innovations in the gate stack of MOS transistors and in on-chip interconnect structures, which result in new and exciting challenges to materials scientists. Memory applications, on the other hand, are driving research and development activities in the field of new materials for challenging capacitor dimensions and for several different concepts of nonvolatile memories.

The scope of this book is to provide an overview of recent developments and research activities in the field of materials used for IT, with a particular emphasis on future applications. Topics are materials for silicon-based semiconductor devices (including high-k gate dielectric materials), materials for nonvolatile memories, materials for on-chip interconnects and interlayer dielectrics (including silicides, barrier materials and low-k dielectric materials), materials for assembly and packaging, etc. The latest results in materials science and engineering as well as applications in semiconductor industry are covered including the synthesis of blanket and patterned thin-film materials, their properties, composition, and structure. Computer modeling and analytical techniques to characterize thin-film structures are included. In this book, material transitions that are necessary to improve the

product performance and to maintain the reliability of products for IT applications are highlighted.

In Chapter 1, the synthesis and properties of ultrathin films for devices are described. Material approaches that are focused on an increase in transistor performance are addressed. In particular, the reduction of gate leakage currents by the implementation of high-k materials (at first silicon oxynitrides, followed by metal oxides) for gate dielectrics in MOS transistors and the increase of the charge mobility in the transistor channel by strained silicon are discussed. Novel concepts such as selective air-gaps and self-assembled monolayers are also included as potential approaches to extend the boundaries of current microelectronic technology.

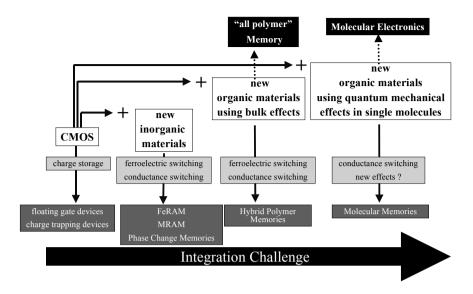

Chapter 2 provides an overview of various material aspects in nonvolatile semiconductor memories. Following a short description and classification of all relevant nonvolatile memory concepts found in research and development today, material optimization in nanocrystal memories that extend the more classical floating gate memories to much smaller feature sizes in the few tens of nanometers range are explained in detail. Recent developments in the three most important nonvolatile RAM concepts, namely ferroelectric memories, magnetoresistive memories and phase change memories, demonstrate the importance of introducing switching mechanism in new materials to achieve improved nonvolatile memory performance. Finally a review of organic memories illustrates the potential new engineering options that arise when organic switching materials are combined with today's advanced silicon electronics.

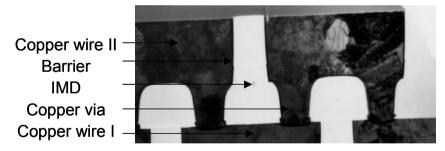

Advanced materials for on-chip interconnects play an important role for performance and reliability of microelectronic products. The scope of Chapter 3 is to provide an overview of recent developments and research activities in the field of materials for the so-called backend-of-line technology, with a particular emphasis on future applications and challenges to materials science and development. The integration of high-conductivity interconnects and of low-k insulating materials is a particular point of focus. Material-related topics are on-chip interconnect materials and barriers, low-k and ultra low-k dielectric materials, nanotubes, etc. The role of microstructure of metal interconnects, particularly texture and stress, on product performance and reliability is presented.

Advanced materials for assembly and packaging play an important role for performance and reliability of microelectronic products, too. In Chapter 4, recent research and development activities, particularly for wafer level packaging and 3D integration, are discussed. Material-related topics are solders, adhesives, encapsulation materials, molding compounds and others for assembly and packaging.

Advanced analytical techniques for thin-film and interface characterization are highlighted in Chapter 5. The continuous improvement of standard techniques and the development of new methods is essential for process development, process control and failure analysis in semiconductor industry. Scientific topics that are addressed range from typical out-of-fab laboratory techniques to synchrotron radiation-based analytics.

This book combines updated selected contributions presented at the EUROMAT 2003 conference in Lausanne, Switzerland, sponsored by the Federation of Euro-

pean Materials Societies FEMS and additional papers from internationally recognized experts in the field from all over the world. The editors would like to thank Peter Paul Schepp of the Deutsche Gesellschaft für Materialkunde DGM, Germany, who actively supported the EUROMAT 2003 topic "Materials for Information Technology" and who encouraged us to prepare this publication.

This book involved the effort of many people. It is primarily based on the strong support and excellent contributions from the authors of the papers. The efficient coordination of the book project by Anthony Doyle, Oliver Jackson and Kate Brown of Springer is gratefully acknowledged. The editors would like to thank Constanze Korn and Tatjana Schmidtchen, AMD Saxony, Dresden, Germany, for their excellent organizational and logistic support and for the enormous amount of work they did to get the camera-ready manuscripts to the publisher on time.

Ehrenfried Zschech Caroline Whelan Thomas Mikolajick December 2004

## List of Contributors

#### V. Beyer

Forschungszentrum Rossendorf Abteilung Strukturdiagnostik P.O. Box 51 01 19 D-01314 Dresden, Germany V.Beyer@fz-rossendorf.de

#### R. Bez

STMicroelectronics, Central R&D Non Volatile Memory Technology Development Via C. Olivetti 2 20041 Agrate Brianza (MI), Italy roberto.bez@st.com

#### H. Brückl

University of Bielefeld Nano Device Group Universitaetsstrasse 25 D-33615 Bielefeld, Germany brueckl@physik.uni-bielefeld.de

#### L. Carbonell

IMEC Advanced Deposition & Removal Technologies Kapeldreef 75 B-3001 Leuven, Belgium carbonel@imec.be

#### **D.** Chrastina

INFM and L-NESS Dipartimento di Fisica, Politecnico di Milano Polo Regionale di Como Via Anzani 52, I-22100 Como, Italy danny@chrastina.net

#### **T.** Conard

IMEC Material and Component Analysis Department Kapeldreef 75 B-3001 Leuven, Belgium tconard@imec.be

#### A. Diebold

SEMATECH Manager Analytical Technology Infrastructure 2706 Montopolis Drive Austin, Texas 78741-6499, USA alain.diebold@sematech.org

#### **T. Dimoulas**

National Center for Scientific Research DEMOKRITOS Institute of Materials Science, MBE Laboratory 153 10, Athens, Greece dimoulas@ims.demokritos.gr

#### M. Engelhardt

Infineon Technologies Corporate Research Otto-Hahn-Ring 6 D-81730 Munich, Germany Manfred.Engelhardt@infineon.com

#### J. P. Guenau de Mussy

IMEC Kapeldreef 75 B-3001, Leuven, Belgium JeanPaul.GueneaudeMussy@imec.be

#### M. Hecker

Leibniz-Institute for Solid State and Materials Research Helmholtzstrasse 20 D-01069 Dresden, Germany M.Hecker@ifw-dresden.de

#### P. Ho

University of Texas at Austin Laboratory for Interconnect and Packaging, UT-PRC 10100 Burnet Road, Bldg 160 Austin, TX 78758, USA paulho@mail.utexas.edu

#### M. Joulaud

MERCK KgaA - CEA Grenoble/LETI 17, Rue des Martyrs 38054 Grenoble, France joulaudmi@chartreuse.cea.fr

#### J. Kittl

IMEC Kapeldreef 75 B-3001 Leuven, Belgium kittlj@imec.be

#### G. Knight

Ottawa-Carleton Institute of Physics c/o Electronic Engineering 1125 Colonel By Drive Ottawa, Ontario K1S 5B6, Canada gknight@doe.carleton.ca

#### J. J.-Q. Lu

Center for Integrated Electronics Rensselaer Polytechnic Institute Troy, New York 12180, USA luj@rpi.edu

#### G. Luyckx

ICI Belgium N.V. Emerson & Cuming Nijverheidsstraat 7 B-2260 Westerlo, Belgium geert.luyckx@nstarch.com

#### M. A. Meyer

AMD Saxony LLC & Co. KG Materials Analysis Department P. O. Box. 11 01 10 D-01330 Dresden, Germany Moritz-Andreas.Meyer@amd.com

#### T. Mikolajick

Infineon Technologies Dresden Flash Technology Predevelopment IFD MDC TD FL2 Koenigsbruecker Strasse 180 D-01099 Dresden Thomas.Mikolajick@infineon.com

#### J. P. Morniroli

Laboratoire de Métallurgie Physique et Génie des Matériaux UMR CNRS 8517, Bâtiment C6 Cité Scientifique 59655 Villeneuve d'Ascq Cédex, France Jean-Paul.Morniroli@univ-lille1.fr

#### M. Nihei

Nanotechnology Research Center, Fujitsu Laboratories Ltd. 10-1 Morinosato-Wakamiya Atsugi 243-0197, Japan nihei.mizuhisa@jp.fujitsu.com

#### H. Oppermann

Fraunhofer IZM Gustav-Meyer-Allee 25 D-13355 Berlin, Germany oppermann@izm.fraunhofer.de

#### V. G. Polovinkin

Institute of Semiconductor Physics pr. Lavrentyev, 13 630090 Novosibirsk, Russia PVG@isp.nsc.ru

#### S. Privetera

Istituto per la Microelettronica e Microsistemi (IMM), CNR Stradale Primosole 50 95121, Catania, Italy stefania.privitera@imm.cnr.it

#### Z. Rahman

University of Limerick Department of Physics Plassey Technological Park Castletroy, Limerick, Ireland Zakia.Rahman@ul.ie

#### F. Shamiryan

IMEC Kapeldreef 75 B-3001 Leuven Belgium Denis.Shamiryan@imec.be

#### N. Rapún

University of Surrey Chemistry Division, SBMS Guildford, Surrey, GU2 7XH, UK N.Rapun@surrey.ac.uk

#### G. Scarel

MDM-INFM National Laboratory Via C. Olivetti 2 20041 Agrate Brianza (MI), Italy giovanna.scarel@mdm.infm.it

#### D. Schmeißer

BTU Cottbus Angewandte Physik / Sensorik Konrad-Wachsmann-Allee 1 D-03046 Cottbus, Germany dsch@tu-cottbus.de

#### J. Schuhmacher

IMEC SPDT-ADRT-FUDIC Kapeldreef 75 B-3001 Leuven, Belgium schuhm@imec.be

#### F. Sediri

Faculté des Sciences de Tunis Département de Chimie Campus Universitaire 2092 Elmanar I, Tunisia faouzi.sediri@ipeit.rnu.t

#### C. Whelan

IMEC SPDT-ITTO Kapeldreef 75 B-3001 Leuven, Belgium whelan@imec.be

#### V. Sukharev

LSI Logic 1501 McCarthy Blvd. MS AE-187 Milpitas, CA 95035 vsukhare@lsil.com

#### Z. Tőkei

IMEC Kapeldreef 75 B-3001, Leuven, Belgium zsolt@imec.be

#### M. Töpper

Fraunhofer IZM Gustav-Meyer-Allee 25 D-13355 Berlin, Germany toepper@izm.fhg.de

#### R. Waser

Forschungszentrum Jülich Departemt IFF & CNI D-52425 Jülich r.waser@fz-juelich.de

#### O. Winkler

Aachen University Institute of Semiconductor Electronics Sommerfeldstrasse 24 D-52074 Aachen, Germany winkler@iht.rwth-aachen.de

#### Y. Yang

University of California Los Angeles Department of Materials Science and Engineering, Los Angeles, CA 90095, USA yangy@ucla.edu

#### P. Zaumseil

IHP Im Technologiepark 25 D-15236 Frankfurt (Oder), Germany Zaumseil@ihp-microelectronics.com

#### I. Zienert

AMD Saxony LLC & Co. KG Materials Analysis Department P. O. Box 11 01 10 D-01330 Dresden, Germany Inka.Zienert@amd.com

# **List of Contents**

# Chapter 1: Recent Advances in Thin-Film Deposition

| Molecular-beam Deposition of High-k Gate           |    |

|----------------------------------------------------|----|

| Dielectrics for Advanced CMOS                      | 3  |

| A. Dimoulas                                        |    |

|                                                    |    |

| LEPECVD — A Production Technique for SiGe          |    |

| MOSFETs and MODFETs                                | 17 |

| D. Chrastina, B. Rössner, G. Isella, H. von Känel  |    |

| J. P. Hague, T. Hackbarth, HJ. Herzog,             |    |

| KH. Hieber, U. König                               |    |

| Thin-film Engineering by Atomic-layer Deposition   |    |

| for Ultra-scaled and Novel Devices                 | 31 |

| G. Scarel, M. Fanciulli                            |    |

| Atomic-layer Deposited Barrier and Seed Layers     |    |

| for Interconnects                                  | 39 |

| J. Schuhmacher, A. Martin, A. Satta, K. Maex       |    |

| Copper CVD for Conformal Ultrathin-film Deposition | 51 |

| M. Joulaud, P. Doppelt                             |    |

| Pushing PVD to the Limits — Recent Advances        | 61 |

| Zs. Tőkei                                          |    |

| Surface Engineering Using Self-assembled Monolayers:<br>Module Substrates for Atomic-layer Deposition<br>C. M. Whelan, AC. Demas, A. Romo Negreira,                           | 69  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| T. Fernandez Landaluce, J. Schuhmacher,<br>L. Carbonell, K. Maex                                                                                                              |     |

| Selective Airgaps: Towards a Scalable Low-k Solution<br>J. P. Gueneau de Mussy, G. Beyer, K. Maex                                                                             | 77  |

| Silicides — Recent Advances and Prospects<br>J. A. Kittl, A. Lauwers, O. Chamirian, M. A. Pawlak,<br>M. Van Dal, A. Veloso, K. G. Anil, G. Pourtois,<br>M. De Potter, K. Maex | 85  |

| <b>TEM Characterization of Strained Silicon</b><br>J. P. Morniroli, P. H. Albarède, D. Jacob                                                                                  | 99  |

| Chapter 2: Material Aspects of Non-Volatile Memories                                                                                                                          |     |

| <b>An Introduction to Nonvolatile Memory Technology</b><br><i>T. Mikolajick, CU. Pinnow</i>                                                                                   | 111 |

| Floating-dot Memory Transistors on SOI Substrates<br>O. Winkler, M. Baus, M. C. Lemme, R. Rölver,<br>B. Spangenberg, H. Kurz                                                  | 127 |

| Ion-beam Synthesis of Nanocrystals for Multidot<br>Memory Structures<br>V. Beyer, J. von Borany                                                                               | 139 |

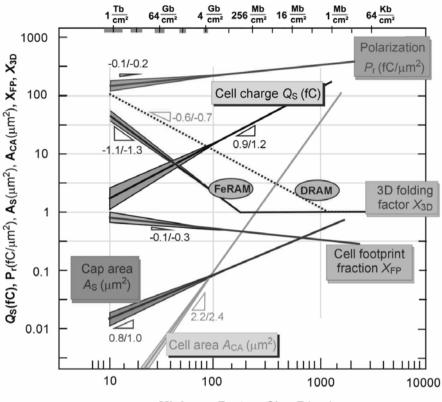

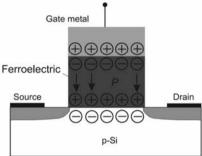

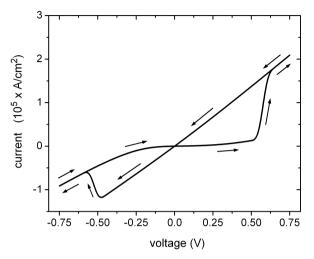

| Scaling of Ferroelectric-based Memory Concepts<br>R. Waser                                                                                                                    | 149 |

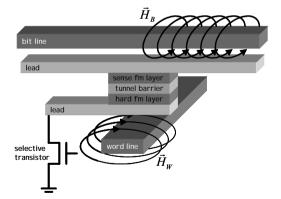

| <b>Device Concepts with Magnetic Tunnel Junctions</b><br><i>H. Brückl, J. Bornemeier, A. Niemeyer, K. Rott</i>                                                                | 163 |

| Phase-change Memories<br>R. Bez, A. Pirovano. F. Pellizzer                                                                                                                    | 177 |

| <b>Amorphous-to-fcc Transition in GeSbTe Alloys</b><br>S. Privitera, C. Bongiorno, E. Rimini, R. Zonca                                                                        | 189 |

| <b>Organic Nonvolatile Memories</b><br>Y. Yang, L. Ma, J. Ouyang, J. He, H. M. Liem,<br>CW. Chu, A. Prakash                                                                         | 197 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 3: Materials for Interconnects                                                                                                                                              |     |

| Interconnect Technology — Today, Recent Advances<br>and a Look into the Future<br>M. Engelhardt, G. Schindler, W. Steinhögl,<br>G. Steinlesberger, M. Traving                       | 213 |

| Dielectric and Scaling Effects on Electromigration<br>for Cu Interconnects.<br>P. S. Ho, KD. Lee, J. W. Pyun, X. Lu, S. Yoon                                                        | 225 |

| <b>Texture and Stress Study of Sub-Micron Copper Inter-</b><br><b>connect Lines using X-ray Micro Diffraction</b><br><i>I. Zienert, H. Prinz, H. Geisler, E. Zschech</i>            | 241 |

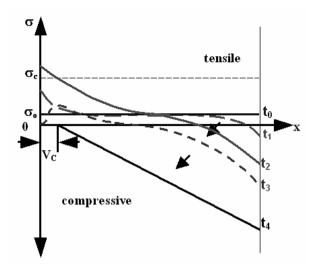

| <b>Stress Modeling for Copper Interconnect Structures</b><br>V. Sukharev                                                                                                            | 251 |

| Conductivity Enhancement in Metallization<br>Structures of Regular Grains<br>G. D. Knight                                                                                           | 265 |

| Advanced Barriers for Copper Interconnects.<br>M. Hecker, R. Hübner, J. Acker, V. Hoffmann,<br>N. Mattern, R. Ecke, S. E. Schulz, H. Heuer,<br>C. Wenzel, HJ. Engelmann, E. Zschech | 283 |

| Synthesis and Characterization of Compounds<br>Obtained by Crosslinking of Polymethyl-<br>hydrosiloxane by Aromatic Rings<br><i>F. Sediri, F. Touati, N. Gharbi</i>                 | 297 |

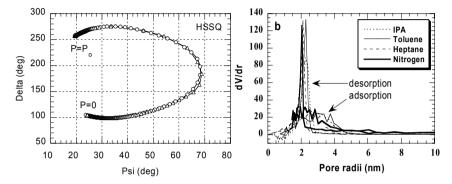

| Revealing the Porous Structure of Low-k Materials<br>through Solvent Diffusion<br>D. Shamiryan, M. R. Baklanov, K. Maex                                                             | 305 |

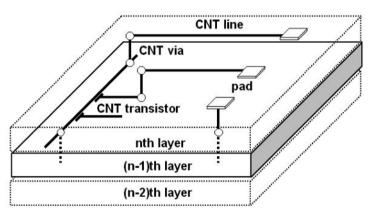

| Carbon Nanotube via Technologies for Future<br>LSI Inteconnects<br>M. Nihei, A. Kawabata, M. Horibe, D. Kondo,<br>S. Sato, Y. Awano        | 315 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Nickel Nanowires Obtained by Template Synthesis<br>I. Z. Rahman, K. M. Razeeb, M. A. Rahman                                                | 327 |

| Chapter 4: Materials for Assembly/Packaging                                                                                                |     |

| <b>The Importance of Polymers in Wafer-Level Packaging</b><br><i>M. Töpper</i>                                                             | 347 |

| Electrically Conductive Adhesives as Solder Alternative:<br>A Feasible Challenge<br>G. Luyckx, G. Dreezen                                  | 363 |

| <b>The Role of Au/Sn Solder in Packaging</b><br>H. Oppermann                                                                               | 377 |

| Packaging Materials: Organic–Inorganic Hybrids<br>for Millimetre-Wave Optoelectronic<br>N. Rapún                                           | 391 |

| Wafer-Level Three-Dimensional Hyper-Integration<br>Technology Using Dielectric Adhesive Wafer Bonding<br>JQ. Lu, T. S. Cale, R. J. Gutmann | 405 |

| Chapter 5: Advanced Materials Characterization                                                                                             |     |

| Challenges to Advanced Materials Characterization |     |

|---------------------------------------------------|-----|

| for ULSI Applications                             | 421 |

| A. C. Diebold                                     |     |

| Advanced Material Characterization by TOFSIMS     |     |

| in Microelectronics                               | 437 |

| T. Conard, W. Vandervorst                         |     |

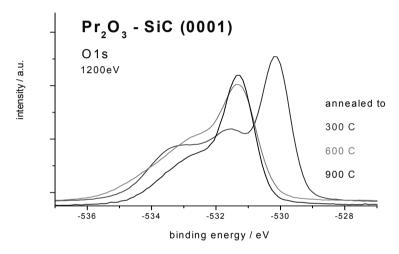

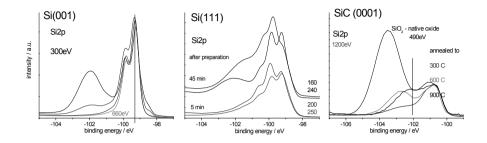

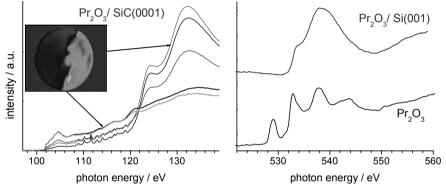

| Electronic Properties of the Interface Formed by Pr <sub>2</sub> O <sub>3</sub> Growth on Si(001), Si(111) and SiC(0001) |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| Surfaces                                                                                                                 | 449 |

| D. Schmeißer, P. Hoffmann, G. Beuckert                                                                                   |     |

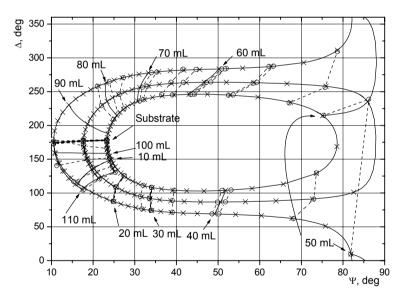

| Materials Characterization by Ellipsometry                                                                               | 461 |

| V. G. Polovinkin, M. R. Baklanov                                                                                         |     |

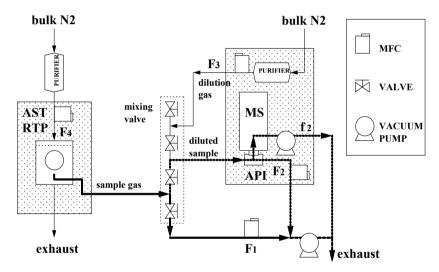

| Thermal Desorption Spectrometry as a Method                                                                              |     |

| of Analysis for Advanced Interconnect Materials                                                                          | 475 |

| L. Carbonell, A. M. Hoyas, C. M. Whelan, G. Vereecke                                                                     |     |

| Electron Backscatter Diffraction: Application                                                                            |     |

| to Cu Interconnects in Top-View and Cross Section                                                                        | 485 |

| M. A. Meyer, I. Zienert, E. Zschech                                                                                      |     |

| X-ray Reflectivity Characterisation of Thin-Film and                                                                     |     |

| Multilayer Structures                                                                                                    | 497 |

| P. Zaumseil                                                                                                              |     |

# Molecular-beam Deposition of High-k Gate Dielectrics for Advanced CMOS

#### A. Dimoulas

MBE Laboratory, Institute of Materials Science, Athens / Greece

#### Introduction

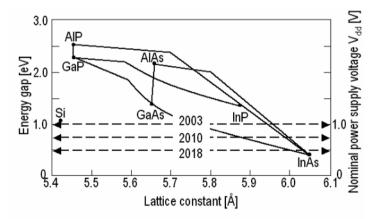

Aggressive scaling to the nanometer range has moved the semiconductor and ICs industry into a period of revolutionary change in materials, device architecture, device processing and tooling. The main driving force behind these changes is the need to increase the on-state (drive) current, and therefore the high frequency performance of logic devices, in order to obtain intrinsic MOSFET gate delay times in the range of picoseconds (or terahertz performance levels) well before the end of the decade [1]. To achieve high drive currents in excess of 1 mA/µm (see Table 1), it is necessary to combine improvements in gate-length scaling, equivalent oxide thickness (EOT), threshold voltage and channel mobility. Intel, the leading ICs manufacturer, has announced [2] that 45 nm CMOS, which will be in production by year 2007 will have advanced high-k dielectric/metal electrode stacks in the gate. Using high- $\kappa$  gate dielectrics with large physical thickness (around 3 nm) it is possible to scale down EOT to less than 1 nm maintaining the gate leakage current at acceptable levels below 1 A/cm<sup>2</sup> [3]. However, transistors with advanced highκ gate stacks suffer from mobility degradation for reasons which are not fully understood at the present time. To overcome this problem, typically a starting chemical oxide (SiO<sub>2</sub>) layer of at least 4 Å is first deposited [3] before the high- $\kappa$ . This improves channel mobility but limits further scaling for more advanced technologies of the 32 and 22 nm node where EOT as low as 5 Å is required (Table 1). For such low EOT values, ultimately clean interfaces are needed which could be obtained by epitaxial oxides on Si. An alternative is to use mobility enhancing channels such as strained Si or replace completely Si by high mobility semiconductors such as Ge or III-V compounds.

McKee *et al.*, [4] at ONRL have pioneered the growth of high-k crystalline oxides on silicon by molecular beam epitaxy (MBE), working with the cubic perovskite SrTiO<sub>3</sub> (STO) on Si (001). Researchers from EPFL [5] and IBM-Zurich [5], IBM/T.J. Watson Res. Center [6, 7] and Toshiba [8] have shown that the fluorite-like oxides such as La<sub>2</sub>Zr<sub>2</sub>O<sub>7</sub>, (La<sub>x</sub>Y<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> and CeO<sub>2</sub>, respectively, can be grown epitaxially on Si (111). However, for gate dielectric applications in Si-based transistor devices, it is necessary to grow epitaxial oxides directly on (001)oriented Si, which has been the favourite substrate orientation of the semiconductor industry for many years. It has been shown that Y<sub>2</sub>O<sub>3</sub> [9–12] and rare earth oxides with cubic symmetry such as Pr<sub>2</sub>O<sub>3</sub> [13] can be grown crystalline on Si (001). However, they adopt an unfavourable orientation (110)<sub>Re2O3</sub>//(001)<sub>Si</sub>, which gives rise to twinning and other defects [11]. Until now, SrTiO<sub>3</sub> was the only known oxide grown by MBE on Si (001) with acceptable epitaxial quality, although rotated in-plane by 45° in order to match the substrate lattice parameters [4, 14, 15]. Very recently [16], A. Dimoulas *et al.*, at NCSR have shown that the pyrochlore  $La_2Hf_2O_7$  (LHO) can be grown crystalline on Si (001) in a cube-on-cube local epitaxial mode forming ultimately clean interfaces with Si.

Table 1. Technology requirements for mainstream logic devices

| Tech. nodes                      | 90 nm                  | 65 nm                  | 45 nm                                            | 32 nm                                               | 22 nm            |

|----------------------------------|------------------------|------------------------|--------------------------------------------------|-----------------------------------------------------|------------------|

| Production                       | 2003                   | 2005                   | 2007                                             | 2009                                                | 2011             |

| Gate stack                       | SiO <sub>2</sub> /poly | SiO <sub>2</sub> /poly | High-κ/metal<br>Chemical oxide<br>starting layer | High-κ/metal<br>Direct epitaxy ?<br>κ~30            |                  |

| Channel                          | Strained Si<br>planar  | Strained Si<br>planar  | 3D Multi-gate?                                   | -Strained Si<br>-high mobility<br>Semiconductors (O | ►<br>Ge, III-V ) |

| Physical gate<br>length (nm)     | 37                     | 25                     | 18                                               | 13                                                  | 9                |

| EOT (nm)                         | 1.2                    | 0.8                    | 0.7                                              | 0.6                                                 | 0.5              |

| Drive current<br>NMOS<br>(mA/µm) | 1.2                    | 1.5                    | 1.9                                              | 2.1                                                 | 2.4              |

#### Front-end Technology for High Performance Logic

Germanium MOSFETs with high-k gates may provide an alternative solution for future high performance logic devices (see Table 1) since the (low-field) mobility of carriers in Ge is three times higher than that in Si. In addition, activation annealing of dopants can be performed at lower temperatures (around 500°C), while the smaller energy gap of Ge allows supply voltage  $V_{dd}$  scaling for reduced power consumption. Finally, monolithic integration with III–V optoelectronics is possible, adding functionality to the chip. Self-aligned n-type Ge MOSFETs with Ge oxynitride/LTO/W gates [17] and p-type Ge MOSFETs with ZrO<sub>2</sub> [18], Al<sub>2</sub>O<sub>3</sub> [19] and HfO<sub>2</sub> [20] high-k gates have been demonstrated. Materials issues have been investigated in detail [21–26], including surface treatment prior to growth [21], band offsets [25] of HfO<sub>2</sub> with Ge and stability of HfO<sub>2</sub> on Ge after hightemperature treatment [26].

In this article, the MBE growth, and the structural and electrical properties of crystalline and amorphous LHO high-k material and its interface with Si(001) are reviewed. In addition, the growth and electrical behaviour of  $HfO_2$  on Ge(001) are reported.

#### Oxide Molecular-beam Epitaxy/(Deposition) Methodology

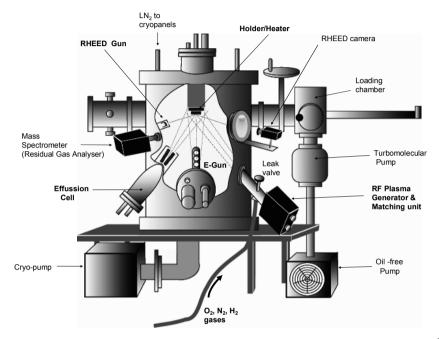

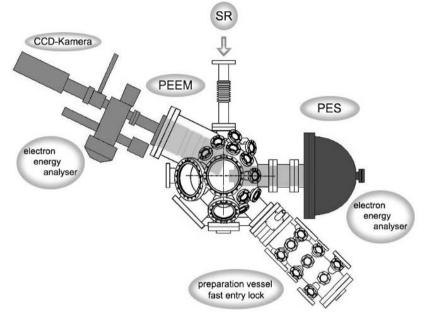

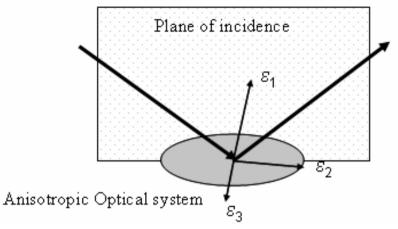

It is well-known that MBE/(MBD) is an excellent research tool mainly for compound semiconductor (*i.e.* III–V) and SiGe devices for specific applications. In recent years, MBE has emerged as a good candidate tool for the front-end processing of mainstream Si-based devices. Oxide MBE can be used to deposit high-k gate dielectrics on semiconductors. A schematic is shown in Figure 1 below.

Figure 1. Molecular beam epitaxy UHV system and components. Base pressure  $\sim 5 \times 10^{-10}$  Torr.

One of the main components is the RF plasma source used for the generation of atomic oxygen beams with thermal energies, which are reactive enough to oxidize the impinging metals on the substrate at relatively low  $O_2$  partial pressure in the  $10^{-6}$  Torr range. The source can produce also nitrogen and hydrogen atomic beams which can be used for surface treatment prior to growth in order to improve the electrical properties of the interfaces. Because MBE is a UHV technique it is possible to use reflection high energy electron diffraction (RHEED) for the *insitu* real-time monitoring of native oxide desorption, surface treatment and growth.

#### Lanthanum Hafnate on Silicon Substrates

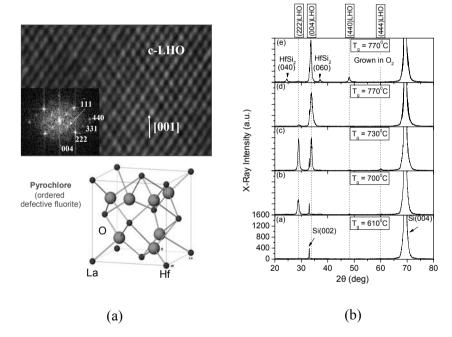

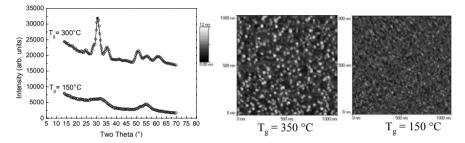

The La<sub>2</sub>Hf<sub>2</sub>O<sub>7</sub> (LHO) material crystallizes in the cubic pyrochlore structure with space group symmetry Fd3m, which is very similar to that of Si (Figure 2 a). This similarity makes LHO a good candidate for epitaxial growth on Si (001), especially since there is good lattice matching between the two materials. The lattice constant of LHO is approximately twice that of Si, with the mismatch being only -0.74 % at room temperature and almost zero at around 800°C. The LHO films are deposited directly on clean, (2×1) reconstructed Si (001) surfaces at several temperatures T<sub>g</sub> in the range between 60°C and 770°C as described in detail elsewhere [16]. Hf and La are co-evaporated from e-beam and effusion cell sources, respectively, in the presence of atomic oxygen beam. The latter is generated by the RF plasma source operating at a power of 350 W with O<sub>2</sub> flow equivalent to a partial pressure of  $4 \times 10^{-6}$  Torr in the chamber.

**Figure 2.** (a) HRTEM image of crystalline LHO grown on Si (100) at 770° C and the digital diffractogram in the inset. The super lattice spots (shown by arrows) indicate an ordered defective fluorite phase (pyrochlore). (b) XRD spectra of LHO grown on Si (100) at different temperatures.

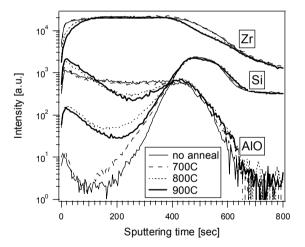

The structural quality of thin LHO films and interfaces depends strongly on the growth temperature  $T_g$ . It can be seen from Figure 2 (b) that the material is amorphous for  $T_g$  lower than 600°C. At higher temperature of about 700°C, the material is polycrystalline with a predominant (111)LHO // (001)Si orientation. When  $T_g$  rises to about 770°C, the LHO film develops a strong preferential orientation

(001)LHO // (001)Si, indicating that this material tends to grow epitaxially when it is prepared at high temperature. When molecular oxygen is used, crystalline  $HfSi_2$  phases are seen (see graph at the top of Figure 2 (b)). This means that reactive atomic oxygen is necessary in order to promote oxidation against competing silicide formation processes.

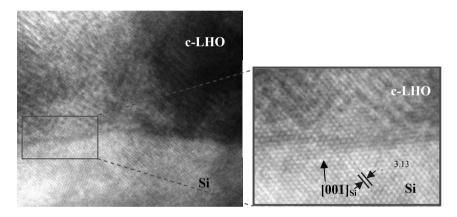

### Crystalline LHO on Si(001) : Ultimately Clean Interfaces

The crystalline LHO grown at the highest temperature of 770°C is shown in Figure 3. The two materials can be distinguished between each other only from the difference in the contrast. Looking at the high magnification picture on the right, the fringes of the {111} lattice planes continue from the Si substrate all the way up to the LHO layer indicating clean interfaces with no interfacial oxide as required for ultimate scaling of devices. This also indicates cube-on-cube epitaxial growth with the  $(001)_{LHO} // (001)_{Si}$  and  $[110]_{LHO} // [110]_{Si}$  orientation relationships. However, the interface and surface morphology is rough, so that additional work is needed in order to optimize growth and obtain device quality layers.

**Figure 3.** HRTEM micrograph showing ultimately clean interfaces between LHO and Si substrates. In the magnification the dotted line shows the lattice fringes of the {111} planes.

## Electrical Properties of Amorphous LHO on Si(001)

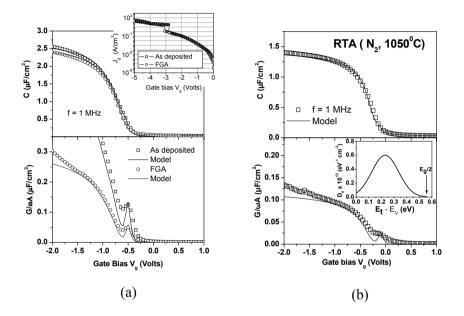

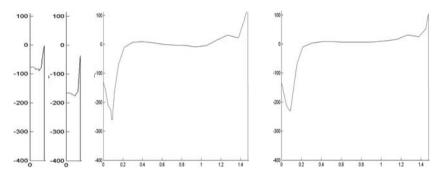

Unlike the case of crystalline LHO, thin films of amorphous LHO deposited by MBD directly on Si are dense and continuous with a smooth surface morphology. They have a dielectric permittivity  $k_{LHO}$  of about 18 [27]. In order to investigate the electrical quality of the films at low EOT, Mo gates were sputtered and subsequently patterned by photolithography and etched using ammonia-based solution to obtain 50 µm square MIS capacitors. Standard data acquisition setup was used for admittance and gate current measurements, described elsewhere. The results for the thinnest (3.3 nm) samples are shown in Figure 4. The C-V and G-V data are fitted

simultaneously using a multi-frequency model we have previously developed [18]. This is a self-consistent solution of Poisson–Schrodinger equation in the semiconductor which takes into account the charge due to interface states as boundary condition. The exchange of carriers between the semiconductor and the interface trap states is described by Shockley–Read–Hall statistics. From the fitting, the EOT, the flat band voltage shift  $\Delta V_{FB}$ , the carrier capture cross section  $c_p$ , and the energy distribution of interface density of states  $D_{it}$  are estimated.

**Figure 4.** Electrical data obtained from a p-type MIS with 3.3 nm-thick LHO deposited at 450°C. (a) As-deposited and FGA-annealed C-V and G-V curves at 1 MHz. The gate current density  $J_g vs$  gate bias  $V_g$  in accumulation is shown in the inset. (b), the C-V and G-V curves after RTA treatment. The inset shows the energy distribution of  $D_{it}$  as determined from the simultaneous fitting of the C-V and G-V curves.

The EOT is estimated to be 0.94 nm for as-deposited samples and increases slightly to about 1 nm after forming gas anneal (FGA) at 450°C for 20 min. The maximum value of Dit is about  $3 \times 10^{12}$  cm<sup>2</sup> in as-deposited MIS, decreasing to about  $1 \times 10^{12}$  cm<sup>2</sup> after FGA as can be seen from the decrease of the conductance peak in Figure 4a. The flatband voltage shift  $\Delta V_{FB}$  was found to be -0.5 V, the possible contributions in this shift coming from the workfunction difference  $\Phi_{ms} \sim -0.26$  V and positive fixed oxide charges in the LHO layer. As can be seen in the inset of Figure 4a, the a-LHO behaves as an excellent insulator with only  $2 \times 10^{-3}$  A/cm<sup>2</sup> at -1 V or  $2 \times 10^{-2}$  A /cm<sup>2</sup> at 1 V beyond flatband in accumulation. This is 4-5 orders of magnitude smaller that conventional SiO<sub>2</sub> devices with the same equivalent thickness of 0.94–1 nm. Rapid thermal annealing (RTA) in N<sub>2</sub> at

1050°C improves most of the electrical properties of a-LHO except from EOT. As seen in Figure 4 (b) the curves shift toward more positive voltage, corresponding to  $\Delta V_{FB}$  of -0.23 V which can be explained in terms of workfuncion difference only. This value is very close to the ideal threshold voltage of -0.27 V in n-channel MOSFETs. The maximum density of states after RTA has dropped to  $6 \times 10^{11}$  cm<sup>2</sup> as can be seen from the inset of Figure 4 (b). In addition, no hysteresis is observed in the samples which have received an RTA annealing. However, the EOT is doubled compared to the as-deposited devices, probably because an interfacial low-k layer is formed. It should be noted however, that the high-temperature treatment in this work is not performed under controlled conditions which are typically employed during dopant activation in transistor processing. In addition, the trend in CMOS processing of high- $\kappa$  gates is to perform dopant activation at lower temperature around 900°C, in which case EOT degradation could be avoided.

In summary, a-LHO with a very low leakage current of  $\sim 2 \times 10^{-2}$  at 1V beyond flatband in accumulation and a low EOT around 0.94–1 nm could have an impact in future low standby devices of the 32 nm technology node which require EOT  $\sim 1.1$  nm and gate leakage of  $4 \times 10^{-2}$  A/cm<sup>2</sup>, provided that EOT degradation could be avoided by applying appropriate high-temperature treatment during CMOS transistor processing.

#### Hafnium Oxide on Germanium Substrates

Adequate preparation of Ge substrates prior to deposition is very important in order to obtain HfO<sub>2</sub> films and interfaces with good electrical quality [21]. As an UHV technique, MBD offers *insitu* desorption of the native oxide, which cannot be achieved very easily by other more standard methodologies such as CVD. The substrate is heated to 360°C in vacuum until a (2×1) reconstruction is obtained (see Figure 5) by RHEED, which is indicative of a clean Ge(100) surface. Subsequently, the substrate is heated to 225° C and is exposed to combined nitrogen and oxygen atomic beams for one minute under a weak Ge flux with the aim to produce an ultra-thin GeO<sub>x</sub>N<sub>y</sub> starting layer.

The procedure for this processing step is as follows.  $O_2$  and  $N_2$  gases are mixed before they are introduced in the RF plasma source through a leak valve. By powering the source at ~ 400 W, a bright plasma mode consisting of nitrogen and oxygen atoms is generated in the discharge chamber and then escape into vacuum as atomic beams. Different compositions of the  $GeO_xN_y$  layer can be obtained by varying the composition of the initial gas mixture which can be monitored by the ratio of  $O_2$  and  $N_2$  partial pressures in the chamber using a mass spectrometer. For the experiments reported here, a ratio  $P_{O2}/P_{N2} \sim 2$  is used. It must be noted that the treatment of the clean Ge surface by O and N before HfO<sub>2</sub> deposition is necessary, otherwise the films are either leaky or do not show MOS behaviour.

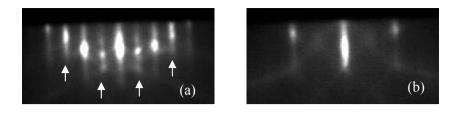

**Figure 5.** RHEED pattern of a clean Ge(100) surface. (a) along the [110] azimuth, (b) along the [100] azimuth, rotated by  $45^{\circ}$ . The weaker spots shown by arrows in (a) are diffraction spots due to (2×1) reconstruction of the surface.

After surface preparation, the substrate is heated to the desired temperature for  $HfO_2$  deposition. Temperatures in the range between 60 and 360°C have been used, since above 360°C the GeO<sub>x</sub>N<sub>y</sub> layer is unstable. The  $HfO_2$  is synthesized on the substrate by evaporating Hf from an e-beam source at a rate of 0.2 A/s in atomic oxygen beams generated by the RF plasma source. The partial pressure of oxygen  $P_{O2}$  during deposition is  $2-4 \times 10^{-6}$  Torr.

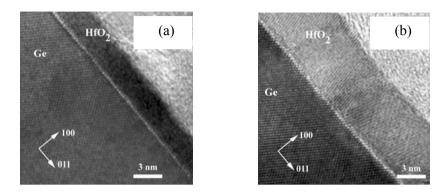

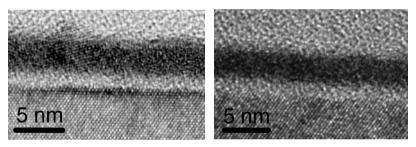

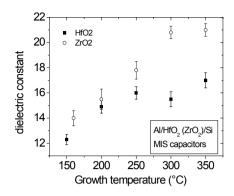

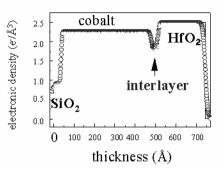

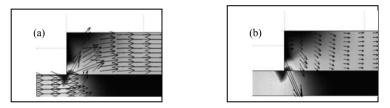

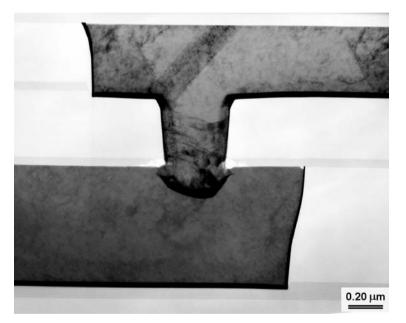

The real images of the  $HfO_2$  films in (110) Ge cross-section are shown in the micrographs of Figure 6 for two samples with thickness 3 and 8 nm which are deposited at 225°C. The thin sample is amorphous while the thick one is polycrystalline. This may be due to re-crystallization occurring during  $HfO_2$  deposition since the thick sample is exposed to elevated temperature for a longer period of time. It is worth noticing from Figure 6 that the interfaces between  $HfO_2$  and Ge are very sharp with the interfacial layer being very thin (1–2 monolayers). This could be expected given that  $GeO_2$  is unstable, preventing reactions of Ge with oxygen at the interface.

#### Electrical Characterization of HfO<sub>2</sub>/Ge M-I-S Capacitors

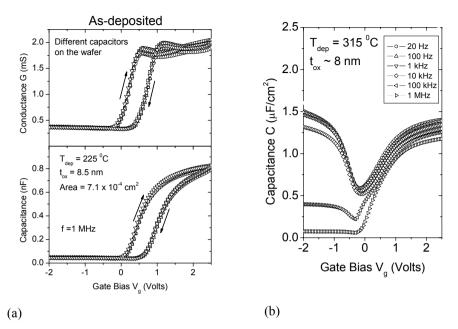

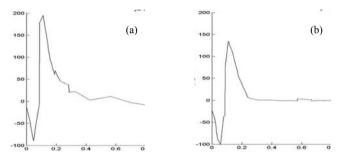

MIS capacitors are prepared by shadow mask and e-beam evaporation of 30 nmthick Pt electrodes to define circular dots, with an area of  $7 \times 1 \cdot 10^{-4}$  cm<sup>2</sup>. Both Sbdoped n-type and Ga-doped p-type substrates were used with resistivity  $\rho \sim 2-5 \Omega \cdot cm$ . The back ohmic contacts are made using eutectic In–Ga alloy. Both p-type and n-type MIS show similar behaviour. Also, the main characteristics of MIS do not depend on the deposition temperature of HfO<sub>2</sub>. Typical C-V and G-V curves for n-type MIS capacitors are shown in Figure 7a. The main characteristics are the rather large hysteresis of about 500 mV and the large ac conductance due to interface states which, however, decreases by a factor of three after forming gas anneal. Figure 7b shows the frequency dependence of the C-V curves for an n-type MIS capacitor. The most characteristic behaviour is the strong frequency dispersion in inversion (negative Vg). The high frequency C-V (*i.e.* 1 kHz) shows lowfrequency behaviour with a high value of the inversion capacitance. This is different from the case of device quality silicon where the 1 kHz capacitance at inversion acquires a small value due to long response time of the minority carriers. The minority carrier response time  $\tau_R$  at room temperature is controlled by generationrecombination processes in depletion, mediated by bulk semiconductor traps. In this case,  $\tau_R \propto 1/n_i$  [28], where  $n_i$  is the intrinsic carrier concentration.

**Figure 6.** HRTEM micrograph in Ge (-110) cross section showing sharp HfO<sub>2</sub>/Ge interfaces. (a)  $t_{ox} \sim 3.1$  nm, (b)  $t_{ox} \sim 8$  nm. The HfO<sub>2</sub> deposition temperature was  $T_{dep}$ =225°C, for both samples.

In Si,  $n_i \sim 1.45 \times 10^{10}$  cm<sup>-3</sup> and  $\tau_R$  ranges between the 0.01 and 1 s, depending on the quality of the material. However, in Ge, due to the smaller band gap,  $n_i$  is more than three orders of magnitude higher ( $n_i \sim 2.4 \times 10^{13}$  cm<sup>-3</sup>), therefore, the response time is expected to be at least three order of magnitude shorter, in the microsecond range, provided that the level of contamination is comparable to that found in device grade Si. This could explain the observed low frequency behaviour of the high frequency (1 kHz) CV curves in Figure 7b.

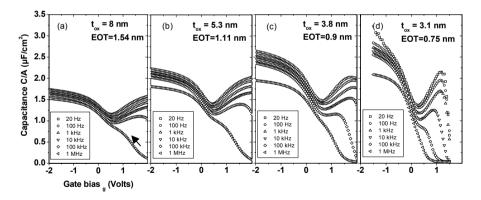

C-V data from p-type MIS capacitors with different HfO<sub>2</sub> thickness are given in Figure 8. As in the case of n-type MIS, there is strong frequency dispersion in inversion (positive  $V_g$ ) and a weak dispersion in accumulation (negative  $V_g$ ). The latter is attributed to a series resistance of ~ 50  $\Omega$ , which mainly affects the 1 MHz curve, lowering the accumulation capacitance.

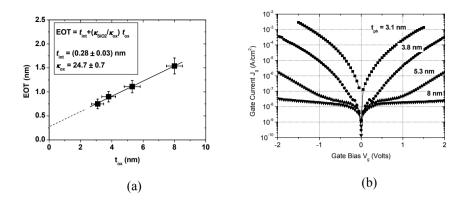

By analyzing of the accumulation capacitance of the low frequency (20 Hz) curves, the EOT is estimated and plotted as a function of the physical oxide thickness in Figure 9a. From this plot, the interfacial thickness  $t_{int}$  is found to be about  $0.28 \pm 0.03$  nm, in agreement with TEM observations, while the dielectric permittivity  $\kappa_{ox}$  of HfO<sub>2</sub> is estimated to be ~  $2.47 \pm 0.7$ . This is close to the expected bulk value and appreciably higher than that obtained from thin films of HfO<sub>2</sub> on Si, which typically ranges between 15 and 20. The gate current J<sub>g</sub> as a function of gate bias V<sub>g</sub> is shown in Figure 9b indicating that the HfO<sub>2</sub> on Ge behaves as an excellent insulator. The thinnest sample with EOT of  $0.75 \pm 0.1$  nm exhibits a very low current of  $4.5 \times 10^{-4}$  A/cm<sup>2</sup> at -1V (accumulation), which are among the best values reported for either HfO<sub>2</sub>/Ge or HfO<sub>2</sub>/Si.

Figure 7. (a) Hysteresis of 1 MHz C-V and G-V curves of n-type MIS. (b) Frequency dependence of C-V curves for n-type  $HFO_2/Ge$  M-I-S capacitors.

**Figure 8.** C-V curves for as-deposited p-type M-I-S with different thickness of  $HfO_2$  dielectric. The scale and axes labels for graphs (b) to (d) are the same with the ones shown with the graph (a).

**Figure 9.** (a) Equivalent (EOT) *vs* physical oxide thickness  $t_{ox}$ . The dielectric permittivity  $\kappa_{ox}$  and the interfacial layer thickness  $t_{int}$  can be estimated from the slope and the intersection with the y-axis, respectively. (b) The gate current  $J_g$  *vs* the applied gate bias  $V_g$  for several MIS with different HfO<sub>2</sub> thickness.

#### Summary

Advanced high-k gate dielectric stacks directly deposited on Si or high mobility semiconductors such as Ge by MBE may offer the solution for aggressive scaling of future nanoelectronic devices. A new high-k dielectric, the pyrochlore La<sub>2</sub>Hf<sub>2</sub>O<sub>7</sub>, has been systematically investigated. This material can be prepared on Si(001) in a cube-on-cube epitaxial mode at high temperature around 770°C forming ultimately clean interfaces with the substrate. At lower temperature the material is amorphous having leakage current four to five orders of magnitude lower than conventional SiO<sub>2</sub> with the same equivalent oxide thickness (EOT) of about 1 nm. Further scaling is expected to be difficult since only moderate values of the dielectric permittivity k around 18 can be obtained. On the other hand, HfO<sub>2</sub> prepared by MBD on Ge(001) substrates forms sharp interfaces and has a relatively high  $\kappa \sim 25$  which is close to the expected bulk value. Low EOT values around 0.75 nm have been obtained at very low leakage current of  $4.5 \times 10^{-4}$  A/cm<sup>2</sup> at 1 V in accumulation. The observed low frequency behaviour of the high frequency (i.e 1 kHz) C-V curves in inversion was attributed to the high intrinsic carrier concentration in Ge due to the small energy band gap.

#### Acknowledgements

I would like to thank my students G. Vellianitis and G. Mavrou and my colleagues Drs. A. Travlos and N. Boukos at NCSR DEMOKRITOS, Prof. E. Evangelou of the University of Ioannina and Drs J.C. Hooker and Z.M. Rittersma of Philips Research Leuven for their contribution in this work.

#### References

- 1. 2003 Edition of the ITRS, International Technology Roadmap for Semiconductors (ITRS), Semiconductor International Association (2003), http://public.itrs.net/

- 2. R. Chau, International Workshop on Gate Insulators, Tokyo, Nov 6–8 (2003)

- W. Tsai, L. Ragnarsson, P.J. Chen, B. Onsia, R.J. Carter, E. Cartier *et al.*, Symposium on VLSI Technology Digest of Technical Papers, Kyoto, 21–22 (2003).

- 4. McKee, F.J. Walker, M. Chisholm, Phys. Rev. Lett. 81, 3014 (1998)

- 5. J. W. Seo, J. Fompeyrine, A Guiller, G. Norga, C. Marchiori, H. Siegwart *et al.*, Appl. Phys. Lett. 83, 5211 (2003)

- 6. S. Guha, N.A. Bojarczuk, V. Narayanan, Appl. Phys. Lett. 80, 766 (2002)

- N.A Bojarczuk, M. Copel, S. Guha, V. Narayanan, E.J. Preisler, F.M. Ross *et al.*, Appl. Phys. Lett. 83, 5443 (2003)

- Y. Nishikawa, N. Fukushima, N. Yasuda, K. Nakayama, S. Ikegawa, Japan J. Appl. Phys. 41, 2480 (2002)

- 9. A. Dimoulas, A. Travlos, G. Vellianitis, N. Boukos, K. Argyropoulos, J. Appl. Phys. 90, 4224 (2001)

- A. Dimoulas, G. Vellianitis, A. Travlos, V. Ioannou-Sougleridis, A.G. Nassiopoulou, J. Appl. Phys. 92, 426 (2002)

- 11. G. Apostolopoulos, G. Vellianitis, A. Dimoulas, M. Alexe, R. Scholz, M. Fanciulli *et al.*, Appl. Phys. Lett. 81, 3549 (2002)

- 12. V. Ioannou-Sougleridis, G. Vellianitis, A. Dimoulas, J. Appl. Phys. 93, 3982 (2003)

- 13. Fissel, H.J. Osten, E. Bugiel, J. Vac. Sci. Technol. B 21, 1765, and references therein (2003)

- 14. K. Eisenbeiser, J.M. Finder, Z. Yu, J. Ramdani, J.A. Curless, J.A. Hallmark, et al., Appl. Phys. Lett. 76, 1324 (2000)

- 15. Norga, A. Guiller, C. Marchiori, J.-P. Locquet, H. Siegwart, D. Halley *et al.*, Mat. Res. Soc. Symp. Proc. 786, (2004)

- 16. Dimoulas, G. Vellianitis, G. Mavrou, G. Apostolopoulos, A. Travlos, C. Wiemer *et al.*, Appl. Phys. Lett. 85, October 11 issue (2004)

- 17. H. Shang, K.L. Lee, P. Kozlowski, C. D'Emic, I. Babich, E. Sikorski et al., IEEE EDL 25, 135 (2004)

- C. Chui, S. Ramanathan, B. Triplett, P. McIntyre, K. Saraswat, in IEDM Tech. Dig., 437–439 (2002)

- 19. D.S. Yun, C.H. Huang A. Chin, W.J. Chen, C.X. Zhu, B.J. Cho et al., IEEE EDL 25, 138 (2004)

- 20. Ritenour, S.Yu, M.L. Lee, N. Lu, W. Bai, A. Pister et al., IDEM Tec. Dig. 2003

- 21. Chui, H. Kim, P.C. McIntyre, K.C. Saraswat, IEEE EDL 25, 274 (2004)

- 22. H. Kim, C. Chui, K.C. Saraswat, P.C. McIntyre, Appl. Phys. Lett. 83, 2647 (2003)

- 23. D. Chi, C. Chui, K.C. Saraswat, B.B. Triplett, P.C McIntyre, J. Appl. Phys. 96, 813 (2004)

- 24. J.-H. Chien, N. A. Bojarczuk, Jr., H. Shang, M. Copel, J.B. Hannon *et al.*, IEEE Trans. Electron. Dev. 51, 1441 (2004)

- 25. V.V. Afanas'ev, A. Stesmans, Appl. Phys. Lett. 84, 2319 (2004)

- E.P. Gusev, H. Shang, M. Copel, M. Gribelyuk, C. D'Emic, P. Kozlowski *et al.*, Appl. Phys. Lett. 85, 2334 (2004)

- Apostolopoulos, G. Vellianitis, A. Dimoulas, J.C. Hooker, T. Conard, Appl. Phys. Lett. 84, 260 (2004)

- E.H. Nicolian, J. Brews, in MOS Physics and Technology, Wiley, New York, 139 (1982)

# LEPECVD – A Production Technique for SiGe MOSFETs and MODFETs

D. Chrastina<sup>a</sup>, B. Rössner<sup>a</sup>, G. Isella<sup>a</sup>, H. von Känel<sup>a</sup>, J. P. Hague<sup>b</sup>, T. Hackbarth<sup>c</sup>, H.-J. Herzog<sup>c</sup>, K.-H. Hieber<sup>c</sup>, U. König<sup>c</sup>

<sup>a</sup>INFM and L-NESS Dipartimento di Fisica, Politecnico di Milano, Como / Italy

<sup>b</sup>Department of Physics & Astronomy, University of Leicester, Leicester / UK

<sup>c</sup>DaimlerChrysler AG, Research and Technology, Ulm / Germany

#### Introduction

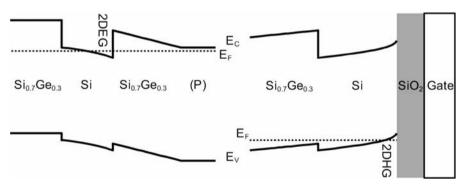

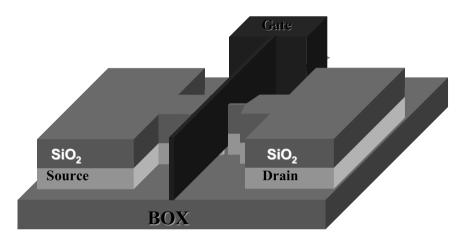

Crystalline silicon germanium alloys greatly extend the potential of silicon-based electronics. Both electron and hole conduction can be enhanced through control of strain, Ge content, and band-gap engineering [1, 2].

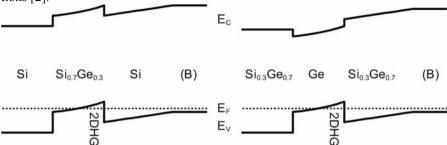

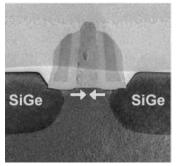

Compressive strain results if  $Si_{1-x}Ge_x$  is deposited epitaxially on  $Si_{1-y}Ge_y$  when x>y, due to the 4.17% mismatch between Ge and Si lattice constants. A compressively strained  $Si_{1-x}Ge_x$  layer forms a quantum well for holes, as shown in the left-hand panel of Figure 1.  $Si_{1-x}Ge_x$  layers with x up to about 0.5 can be grown pseudomorphically (without relaxing the strain imposed by the substrate) on Si, in thicknesses which are useful for electronic applications. However, pure Ge (x=1) cannot generally be deposited directly on a Si substrate (y=0) without a strain-induced transition to a three-dimensional growth (Stranski–Krastanow) mode after a few monolayers [3]. Furthermore, even in the case of two-dimensional (Frank-van der Merwe) growth there is a limit to how much strain can build up before the strained layer relaxes [4].

Therefore, the epitaxial two-dimensional growth of a strained Ge-rich layer  $(x\sim1)$  of useful thickness directly on a Si substrate is not possible. However, such a layer can be grown on a relaxed Si<sub>1-y</sub>Ge<sub>y</sub> buffer layer, with  $0.5 \le y < 1.0$ . The band profile in this case is shown in the right-hand panel of Figure 1. The Si substrate plus a relaxed buffer forms a virtual substrate (VS). A VS also allows the growth of a layer under tensile strain  $(x \le y)$  which creates a quantum well for electrons, as shown in the left-hand panel of Figure 2 [2, 5]. Furthermore, tensile-strained Si surfaces are smoother than unstrained Si surfaces because tension increases the surface step energy [6].

Silicon germanium has become a commercially successful technology. Its most mature manifestation is the heterojunction bipolar transistor (HBT), which has the advantages that it is only a minor modification of the Si bipolar transistor and is easily integrated into standard complementary metal-oxide-semiconductor (CMOS) processes. This is known as BiCMOS. A thin layer of SiGe is deposited pseudomorphically to act as the base of the transistor, and as such this technology is easy to implement. Modern SiGe HBTs can now operate at frequencies above 300 GHz and are used in both radio frequency wireless and cable communications [2].

**Figure 1.** Band profiles of two compressively-strained systems. Left panel: a strained SiGe channel grown pseudomorphically on Si. Right panel: a strained Ge channel grown on a SiGe VS. The growth direction is from left to right, so in both cases, boron doping (B) is above the channel. Holes diffuse into the channel and an electric field is set up between the two-dimensional hole gas (2DHG) and ionized dopant atoms. The dashed line is the Fermi level  $E_F$ , and  $E_C$  and  $E_V$  are the conduction and valence bands, respectively. Band offsets and other parameters can be found in Ref. [5].

**Figure 2.** Band profiles of Si under tensile strain on a relaxed SiGe VS. Left panel: Si under tensile strain forms a quantum well for electrons, so electrons from a phosphorus-doped region (P) diffuse into the Si and a two-dimensional electron gas (2DEG) forms. Right panel: a strained Si surface channel can be biased with a gate, to induce a 2DHG [2, 5].

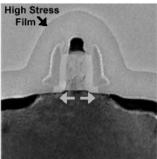

Strained Si on a VS on the other hand requires the VS to have low surface roughness, a high degree of relaxation, and low defect densities [1]. There exist two fundamentally different approaches for realizing VSs with acceptable properties. A well-established solution to this problem is the graded buffer. The basic concept of grading Si<sub>1-x</sub>Ge<sub>x</sub> alloy layers to some final composition *x*, either linearly or step-wise, has proven to be highly successful [7].

Si or Ge quantum wells grown on VSs with thick graded buffers have been demonstrated to have excellent electrical properties [8–10], but there are disadvantages of thick buffers. Firstly, SiGe alloys are poor thermal conductors, leading to problems of heat dissipation for highly integrated circuits. Secondly, long range surface roughness (with  $\sim 1 \ \mu m$  correlation length) due to the so-called "cross-hatch" [11] may cause problems during device processing, and the large step height between regions covered by virtual substrates and bare Si regions hampers integration. Also, a large amount of precursor material is consumed, and in most MBE or CVD systems the growth time is at least a few hours.

For these reasons a second solution is being pursued, which involves thin constant-composition layers. Several concepts have been tried over the past few years to achieve highly relaxed SiGe layers as thin as a hundred nanometers [12, 13]. These methods fall into two categories.

The first involves growth of a Si buffer layer at unusually low substrate temperatures  $T_s$  (around 400°C) before the actual SiGe buffer is deposited at higher  $T_s$  [14-16]. This so-called low-temperature Si (LT-Si) layer contains a large number of point defects, the accumulation of which is believed to promote relaxation [17]. Alternatively, the SiGe buffer layer itself may be grown at very low  $T_s$ (below 200°C) with essentially a similar effect [18]. The disadvantage here is that long periods of thermal cycling may be needed to achieve a stable state of relaxation. Also, such low-temperature growth cannot be realized by chemical vapor deposition (CVD) since growth rates decrease exponentially as  $T_s$  is reduced. Most work in this field has therefore been carried out with molecular-beam epitaxy (MBE) which is not suitable for high volume Si or SiGe production.

The second approach is based on ion implantation of H or He into a strained SiGe layer, and subsequent thermal treatment [19, 20]. This leads to bubble formation, facilitating dislocation loop nucleation close to the Si/SiGe interface. Except for the extra processing steps, this method appears very attractive, but seems to be limited to buffers with Ge content below 30% [20-22]. In a variation of this, Ar ions can be implanted into the Si substrate before SiGe growth [23].

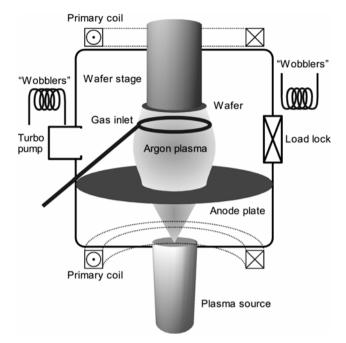

In this chapter we shall discuss an alternative method suitable for high-volume production of both thick graded buffers and thin buffers. This method is called low-energy plasma-enhanced chemical vapor deposition (LEPECVD) [24].

#### LEPECVD

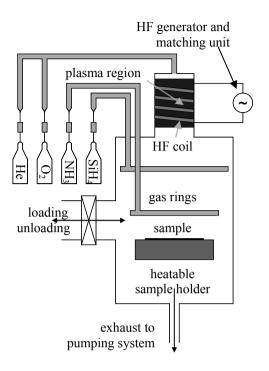

The basic LEPECVD system is shown schematically in Figure 3. A Ta filament in a plasma source attached to the deposition chamber is current-heated to the point of thermionic emission. Ar gas is passed through the source into the chamber, and a high-intensity direct current arc is struck between the source and the chamber. The arc current is of the order of 20-80A but the arc voltage is less than 30 V due to the electron-rich conditions. The plasma is focused onto the substrate with magnetic fields, while the substrate is heated from behind with a graphite heater. Precursor gases are introduced through a ring just below the substrate: SiH<sub>4</sub> and GeH<sub>4</sub> are used for SiGe growth, and PH<sub>3</sub> and B<sub>2</sub>H<sub>6</sub> (both diluted in Ar) are used for doping; H<sub>2</sub> can also be used to fine-tune the surface mobility of adatoms.

**Figure 3.** The low-energy plasma-enhanced chemical vapor deposition (LEPECVD) system. A low-voltage high-current dc discharge is sustained between the source and the anode plate. The substrate is exposed to the plasma, but the ion energies are too low to cause any damage.

Epitaxial growth rates for  $Si_{1-x}Ge_x$  of any composition can be varied arbitrarily from 1 Ås<sup>-1</sup> to almost 10 nms<sup>-1</sup>, at substrate temperatures of 450-750°C. The growth rate is controlled both by varying the precursor gas flows and by changing the plasma arc current and the strength of the magnetic confinement field. The growth rate and film composition are effectively independent of substrate temperature. Around 20% of the precursor material is incorporated into the sample under plasma conditions optimized for high growth rates.

The development of LEPECVD was motivated by the need for relaxed SiGe alloy buffer layers epitaxially grown on Si wafers. In the case of chemical vapor deposition (CVD) without plasma, the gaseous precursors decompose on the growing surface. For Si growth at substrate temperatures below ~800°C, the growth rate is limited by H desorption from the growing surface [25]. In fact, there is an exponential dependence of growth rate on substrate temperature with an activation energy of around 200 kJmol<sup>-1</sup>. The activation energy for desorption of H from a Ge surface is significantly lower, and this leads to a Si<sub>1-x</sub>Ge<sub>x</sub> growth rate that is strongly dependent on x as well as temperature, in a non-trivial way. Typical growth rates are 10-100 nmmin<sup>-1</sup> and less than 1% of the silicon and germanium precursor gases is deposited.

The low energy plasma improves matters in two ways. Firstly, the precursor gases are efficiently decomposed in the plasma column. Secondly, H is desorbed

from the growing surface by ion bombardment. The energy of the ions is however too low ( $\sim 10 \text{ eV}$ ) to cause any damage to the crystalline structure of the substrate.

MBE does not suffer from the problem of growth rate dependence on substrate temperature, but since it is a solid-source process it is unsuitable for the industrial growth of thick layers. Typically, the growth chamber vacuum needs to be broken to replenish the sources after  $\sim$ 5-10 VSs have been grown. SiGe MBE growth rates are also usually of the order of 10-20 nmmin<sup>-1</sup> unless special techniques are used [26].

#### Applications

Virtual Substrates

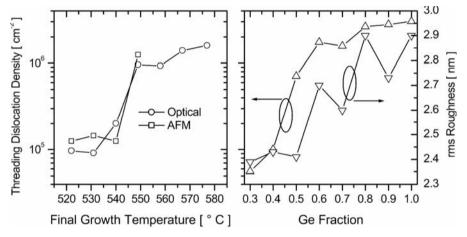

**Figure 4.** Left panel: Threading dislocation density on thick graded (x=0.4) VSs grown by LEPECVD as a function of final growth temperature. The grading rate was 7% per micron and the constant composition cap is 1 µm thick. Etch pits were counted either with an optical microscope or an AFM. Right panel: Surface roughness and threading dislocation density on thick graded VSs grown by LEPECVD, with optimized temperature profiles.

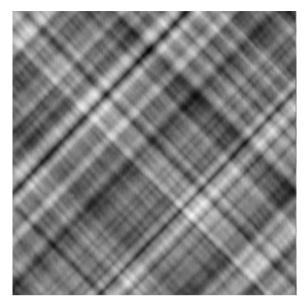

Growth rates in LEPECVD are not strongly dependent on substrate temperature, so the temperature profile during the growth of a thick VS can be varied to optimize the defect density, as shown in the left-hand panel of Figure 4 for thick VSs graded at 7% per micron to a final Ge content of 40%. Generally, the growth temperature should be reduced as the Ge content increases; it can be seen that with a suitably low final temperature, the threading dislocation density can be reduced to less than  $10^5$  cm<sup>-2</sup>. The right-hand panel of Figure 4 shows how the roughness and dislocation density of a VS tend to increase as a function of Ge content, up to  $3 \times 10^6$  cm<sup>-2</sup> for pure Ge. An atomic force microscopy (AFM) image of a thick graded VS (with a final Ge content of 30%) is shown in Figure 5. The rms roughness is 2.6 nm. For comparison, a 50% graded VS grown by UHVCVD has an rms roughness of 37 nm [29].

**Figure 5.** Atomic force microscopy (AFM) image of a 6  $\mu$ m thick VS graded from 0 to 30% (sample 7208). The image size is 25×25  $\mu$ m. Root mean square (rms) roughness is 2.6 nm and the total height range is 15.6 nm.

LEPECVD has also been used to grow thin buffers which are suitable for n-MODFETs [13, 30, 31]. At 500nm, the buffers are 5-10 times thinner than standard graded buffers. The buffers are grown in one step, at a high growth rate and a low substrate temperature. Neither complicated thermal cycling nor ion implantation is required. Chemical–mechanical polishing is also unnecessary.

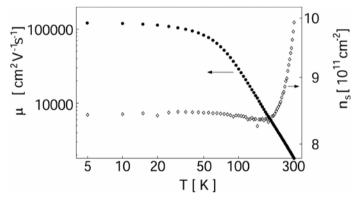

**Figure 6.** Hall mobility (filled symbols) and hole sheet density (open symbols) of a strained Ge p-MODQW structure on a relaxed linearly-graded SiGe buffer (sample 6745).

The combination of high growth rate and low substrate temperature allows a high degree of strain to accumulate in the  $Si_{1-x}Ge_x$  layer during growth, and this

may lead to a higher dislocation glide velocity which facilitates a high degree of relaxation. Molecular dynamics simulations suggest that the nature of the dislocation core is strain dependent [32], with more mobile cores forming under high strain.

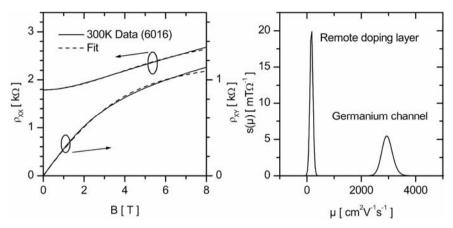

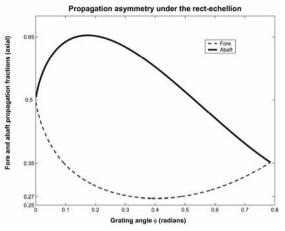

**Figure 7.** Left panel: Longitudinal and transverse magnetoresistance measured at 300K on a strained Ge p-MODQW structure, together with fit from a calculated mobility spectrum [27, 28] shown on the right. Right panel: Mobility spectrum obtained for sample 6016 at 300 K from the magnetoresistance shown on the left. Channel mobility is 2940 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at a hole density of  $5.7 \times 10^{11}$  cm<sup>-2</sup>.

#### Hole Mobility Enhancement

Traditionally, the speed of CMOS has been limited by the poor hole mobility of Si, relative to the electron mobility. Since Ge has one of the highest hole mobilities of any semiconductor, SiGe is an obvious choice for p-channel devices. A complete p-HMOSFET (heterostructure-MOSFET) layer structure with a Ge-rich channel has been grown by LEPECVD [33]. Transistors fabricated on this material demonstrate effective hole mobilities at room temperature which approach the Si electron mobility.

Alloy scattering means that the best hole mobilities should be seen in pure Ge channels [34, 35]. Modulation-doped p-channel quantum wells (p-MODQWs) grown by LEPECVD, with strained Ge channels on Si<sub>0.3</sub>Ge<sub>0.7</sub> VSs, have a maximum low-temperature (2 K) mobility (Figure 6) of 120,000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at a sheet density of  $8.5 \times 10^{11}$  cm<sup>-2</sup>. These structures were front-side doped (with the dopant above the channel). Optimization of the growth temperature and use of hydrogen means that the upper heterointerface was very smooth. The mobility is a factor of two greater than the best p-type Ge channel mobility result demonstrated on material grown by MBE [10]. There, the doping had to be introduced underneath the channel (probably leading to dopant segregation into the channel) since the upper interface was of lower quality due to strain-induced roughening. Our results also evince the quality of the VS, in terms of threading dislocation density and surface roughness.

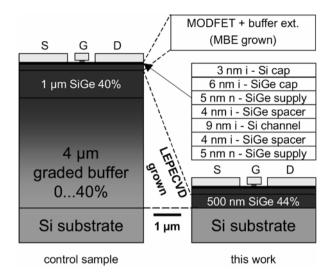

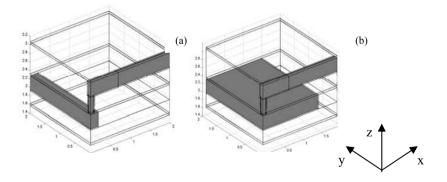

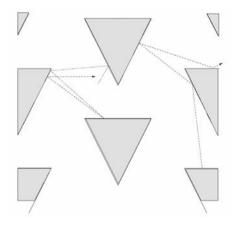

**Figure 8.** Schematic of the MODFET structures grown on a conventional thick graded VS (left) and on the novel thin VS (right), drawn to scale. The inset shows the stack of the active layers. A buffer extension of 150 nm was grown by MBE before the active layers.

Room temperature channel mobilities have been extracted from the magnetic field dependence of the conductivity and Hall coefficient (Figure 7). The right-hand panel of Figure 7 shows a mobility spectrum of a strained Ge p-MODQW structure on a relaxed linearly-graded SiGe buffer (sample 6016) at 300 K, found from the data in the left-hand panel. Two peaks are evident, corresponding to conduction in the strained Ge channel (2940 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and the boron-doped supply layer (180 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>). By integrating these peaks, the carrier sheet densities are found to be  $5.7 \times 10^{11}$  cm<sup>-2</sup> in the channel and  $1.0 \times 10^{13}$  cm<sup>-2</sup> in the supply layer [27, 28]. Similar values for the channel mobility have been found by mobility spectrum analysis in strained Ge structures grown with other techniques [37, 38].

In addition, Si under tensile strain should feature enhanced hole mobility over unstrained Si due to a reduction of effective mass [34]. However, since tensile-strained Si on SiGe does not form a quantum well for holes then a surface channel must be induced using the field effect, as shown in the right-hand panel of Figure 2 [2].

#### Electron-channel Devices

Modulation-doped n-channel FETs (n-MODFETs) and n-MODQWs have been fabricated using a combined LEPECVD+MBE process: a buffer is grown by LEPECVD and then the electrically active structure is grown by solid-source MBE [39-41]. This combines the advantages of LEPECVD (high growth rates for high-quality VS production) with the advantages of MBE (good control of n-type doping and concentration profiles).

The active MODFET layer stack was grown by MBE at a constant temperature of 540°C and a rate of 0.25 nms<sup>-1</sup> for SiGe or 0.15 nms<sup>-1</sup> for Si. The double-sided modulation-doped structure is formed by a 9 nm strained Si channel, embedded in 4 nm doping setback SiGe layers and 5 nm Sb doped SiGe supply layers. Doping was achieved by secondary implantation (DSI) [42]. Device processing included isolation by dry mesa etching, deposition of SiO<sub>2</sub> as a field oxide, window opening by wet chemical etching, P implantation and thermal activation in the ohmic contact region, deposition and lift-off of the Ti/Pt/Au source and drain contacts and finally definition of the Pt/Au Schottky gate by means of electron-beam lithography. The smallest structures have a gate length  $l_G=70$  nm and a source-drain distance  $d_{SD}=1 \mu m$  [30].

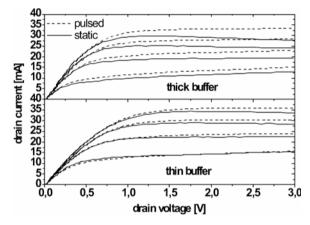

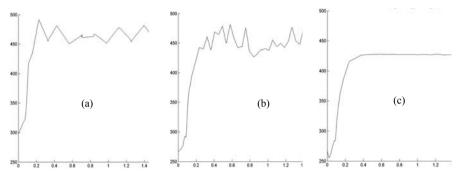

**Figure 9.** Comparison of the MODFET output characteristics on thin and thick relaxed LEPECVD-grown Si<sub>0.6</sub>Ge<sub>0.4</sub> buffers (lower and upper curves, respectively) under static and pulsed conditions. The gate voltage  $V_{\rm G}$  was varied between -0.6 and +0.6V in steps of 0.4V.

A comparison of thick and thin VS structures is shown in Figure 8, and device characteristics are shown in Figures 9 and 10. The lower and upper set of curves in Figure 9 show the I - V characteristics of 100 µm wide devices prepared on the thin and the thick LEPECVD-grown buffer, respectively. The measurements were performed both under static and pulsed conditions. The pulse width was 200 ns. Drain saturation currents I<sub>DSS</sub> of more than 300 mA/mm and a maximum transconductance of  $g_m = 230$  mS/mm have been achieved in both cases. The divergence between the DC and pulsed currents is much larger for the thick buffer. At full enhancement (drain voltage  $V_D=3$  V, gate voltage  $V_G=+0.6$  V) a current difference of 17% can be derived from the uppermost curves, which has to be compared to only 6% in the case of the thin buffer. This indicates a significant reduction of self-heating from the tenfold decrease of buffer thickness. The difference in the self-heating effect by a factor of approximately three is in good agreement with the rough estimation that the thermal resistance of a device on a relaxed SiGe buffer is proportional to the square root of the buffer thickness [43]. Taking this into account a device temperature reduction of 70 K can be estimated by applying the thin VS.

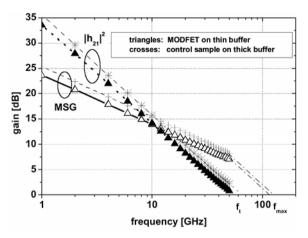

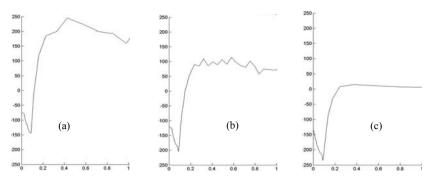

**Figure 10.** De-embedded current gain  $|h_{2l}|$  and maximum stable gain *MSG* spectra of 100 µm wide devices. Transit frequencies of  $f_T$ =55 GHz/63 GHz and maximum frequencies of oscillation  $f_{max}(MSG)$ =113 GHz/128 GHz can be derived for devices on thin and thick VS, respectively.

The current gain  $h_{21}$  and the maximum stable gain (MSG) of 100 µm wide devices are shown in Figure 10. By extrapolating the current gain, a transit frequency  $f_T$ =55 GHz can be derived for the transistors on the thin VS. The results are comparable to the cut-off frequency of the thick buffer control device having an  $f_T$  of 63 GHz. By using the acknowledged procedure of extrapolating MSG with a slope of 10dB/decade up to the point where the stability factor k reaches 1 and further extrapolation of the maximum available MAG with 20 dB/decade, maximum frequencies of oscillation  $f_{max}(MAG)$ =113 GHz and 128 GHz are achieved for the thin and thick buffer device. Assuming reflection-free input and output matching, cutoff frequencies of  $f_{max}(U)$ =138 GHz and 144 GHz can be derived from the 10 dB transits of Masons's gain U (for clarity not shown in Figure 10), respectively. High-frequency performance is not degraded significantly by a ten-fold reduction in buffer thickness; in fact, LEPECVD-grown thin VSs are competitive with thin VSs produced both low-temperature epitaxy and He implantation [13].

## Conclusions

LEPECVD is a new process for epitaxy of SiGe at rates of several nanometres per second. Growth rates are independent of alloy composition and substrate temperature, giving the maximum freedom for optimization of growth parameters. Being a gas source process, it is suitable for industrial production of electronic device-grade material.

High quality n-MODFETs have been produced in mixed LEPECVD+MBE technology [41], and a novel thin VS design (which is made possible by the high growth rates available in LEPECVD even at low substrate temperature) allows access to the advantages of strained Si without the disadvantages of thick graded SiGe layers [30].

High effective mobilities have been demonstrated at room temperature in p-HMOSFETs [33], and exceptional mobilities have been demonstrated in p-MODQW structures at low temperature [36].

## Acknowledgements

Financial support from GROWTH Program ECOPRO No. GRD2-2000-30064 and EC, frame of IST-1999-SIGMUND and German BMBF Project Ultra2 is gratefully acknowledged.

## References

- 1. F. Schäffler. Semicond. Sci. Technol. 12, 1515 (1997)

- 2. D.J. Paul. Semicond. Sci. Technol. 19, R75 (2004)

- Y.-W. Mo, D.E. Savage, B.S. Swartzentruber, M.G. Lagally. Phys. Rev. Lett. 65, 1020 (1990)

- 4. J.W. Matthews, A.E. Blakeslee. J. Cryst. Growth 32, 265 (1974)

- 5. M.M. Rieger, P. Vogl. Phys. Rev. B 48, 14276 (1993)

- 6. Y.H. Xie, G.H. Gilmer, C. Roland, P.J. Silverman, S.K. Buratto, J.Y. Cheng, *et al.* Phys. Rev. Lett. 73, 3006 (1994)

- E.A. Fitzgerald, Y.-H. Xie, M.L. Green, D. Brasen, A.R. Kortan, J. Michel, *et al.* Appl. Phys. Lett. 59, 811 (1991)

- K. Ismail, M. Arafa, K.L. Saenger, J.O. Chu, B.S. Meyerson. Appl. Phys. Lett. 66, 1077 (1995)

- 9. P. Weitz, R.J. Haug, K. von Klitzing, F. Schäffler. Surf. Sci. 361/362, 542 (1996)

- Y.H. Xie, D. Monroe, E. A. Fitzgerald, P.J. Silverman, F.A. Thiel, G.P. Watson. Appl. Phys. Lett. 63, 2263 (1993)

- R.M. Feenstra, M.A. Lutz, F. Stern, K. Ismail, P.M. Mooney, F.K. LeGoues, et al. J. Vac. Sci. Technol. B 13, 1608 (1995)

- 12. T. Hackbarth, H.-J. Herzog, M. Zeuner, G. Höck, E.A. Fitzgerald, M. Bulsara, et al. Thin Solid Films 369, 148 (2000)

- M.E. Aguilar, M. Rodriguez, N. Zerounian, F. Aniel, T. Hackbarth, H.-J. Herzog, *et al.* Solid State Eletron. 48, 1443 (2004)

- 14. H. Chen, L.W. Guo, Q. Cui, Q. Hu, Q. Huang, J.M. Zhou. J. Appl. Phys. 79, 1167 (1996)

- 15. K.K. Linder, F.C. Zhang, J.-S. Rieh, P. Bhattacharya, D. Houghton. Appl. Phys. Lett. 70, 3224 (1997)

- Y.H. Luo, J L. Liu, G. Jin, J. Wan, K. L. Wang, C. D. Moore, et al. Appl. Phys. Lett. 78, 1219 (2001)

- Y. B. Bolkhovityanov, A. K. Gutakovskii, V. I. Mashanov, O. P. Pchelyakov, M. A. Revenko, L. V. Sokolov. Thin Solid Films 392, 98 (2001)

- 18. E. Kasper, K. Lyutovich, M. Bauer, M. Oehme. Thin Solid Films 336, 319 (1998)

- 19. S. Mantl, B. Holländer, R. Liedtke, S. Mesters, H.-J. Herzog, H. Kibbel, *et al.* Nucl. Instr. Meth. B 147, 29 (1999)

- B. Holländer, S. Lenk, S. Mantl, H. Trinkaus, D. Kirch, M. Luysberg, *et al.* Nucl. Instr. Meth. B 175-177, 357 (2001)

- J. Cai, P.M. Mooney, S.H. Christiansen, H. Chen, J.O. Chu, J.A. Ott. J. Appl. Phys. 95, 5347 (2004)

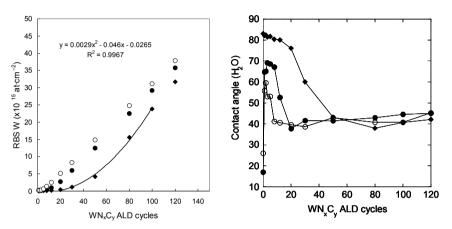

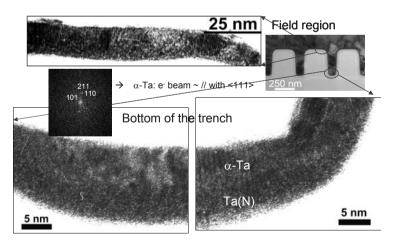

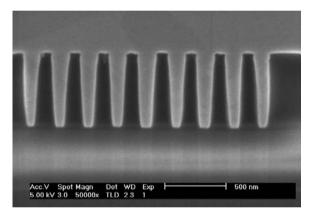

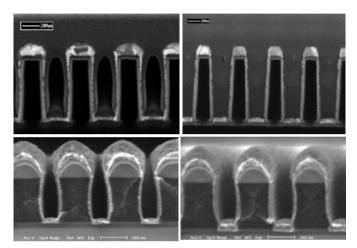

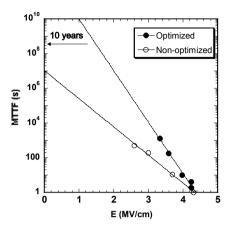

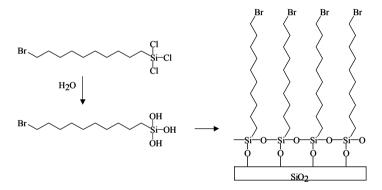

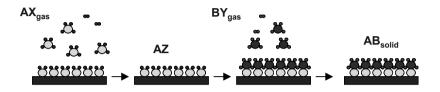

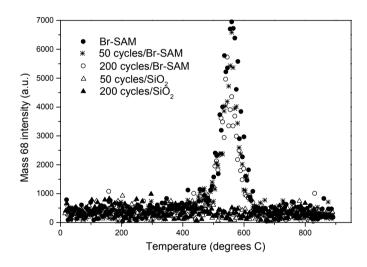

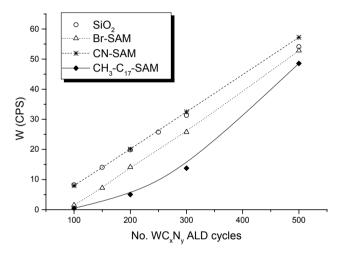

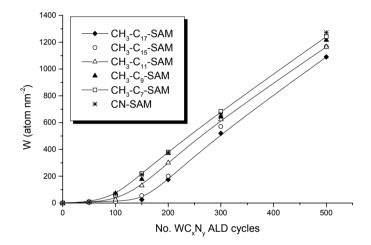

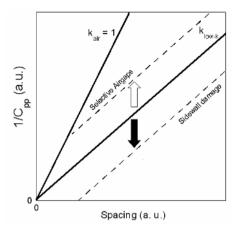

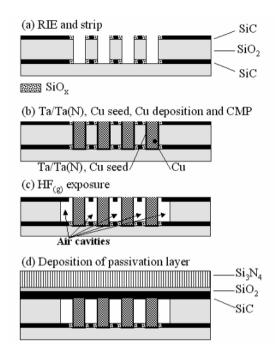

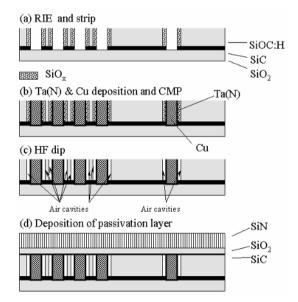

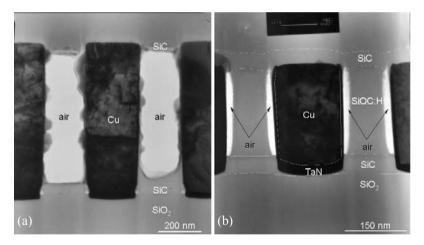

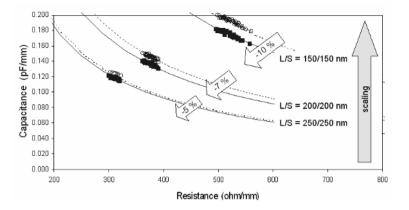

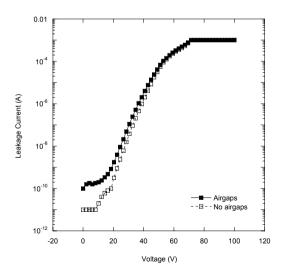

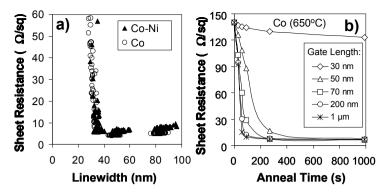

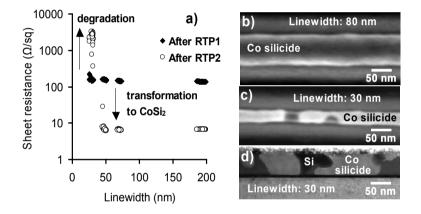

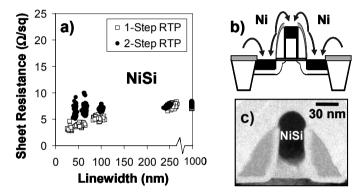

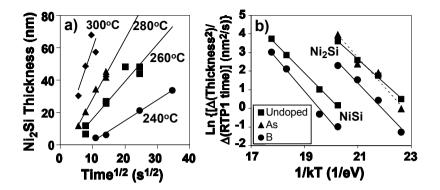

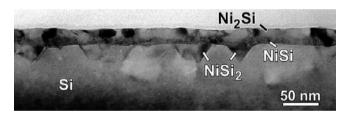

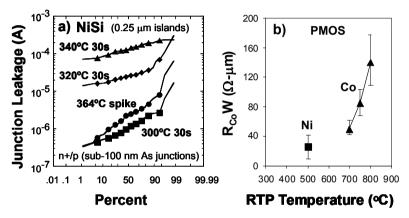

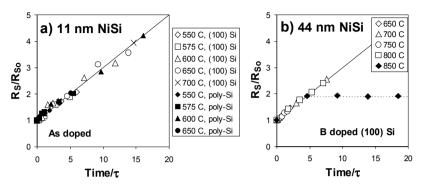

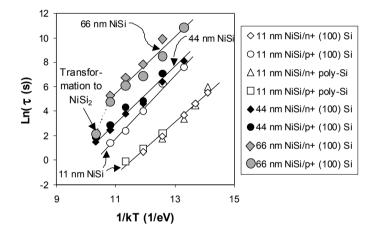

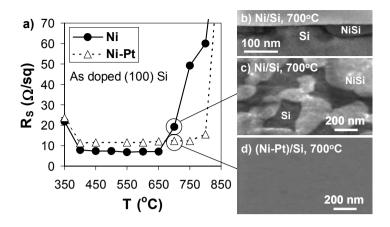

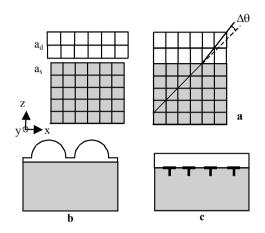

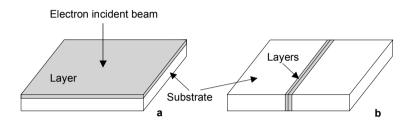

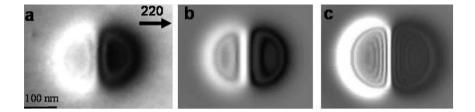

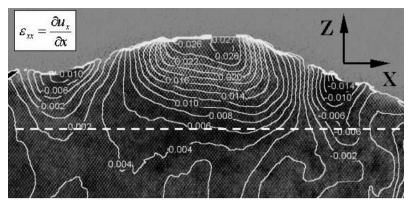

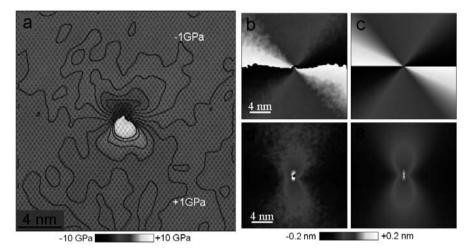

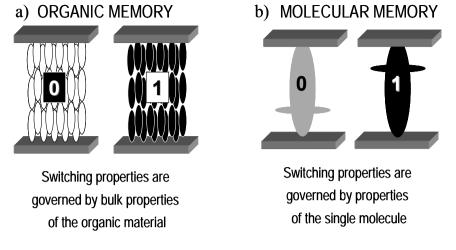

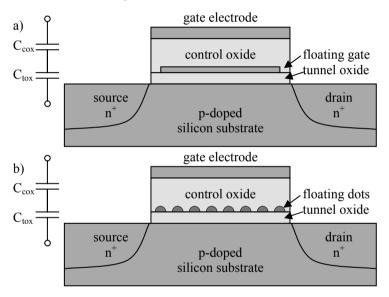

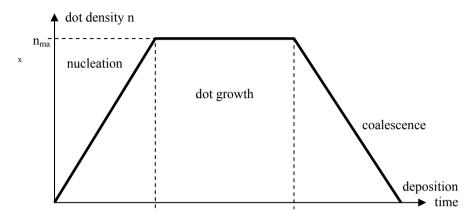

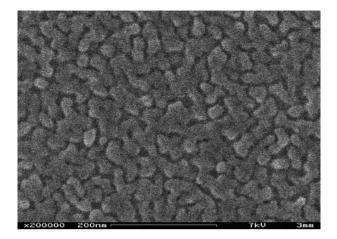

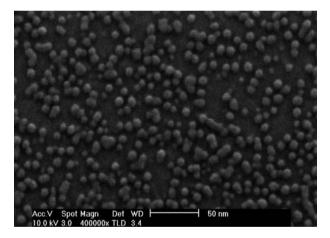

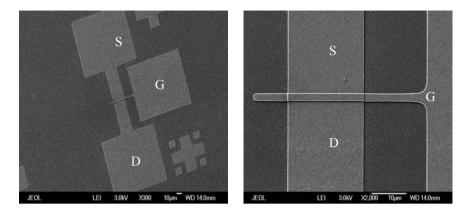

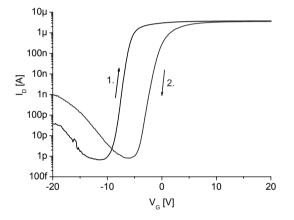

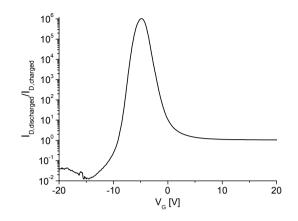

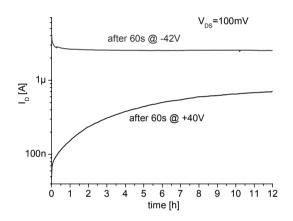

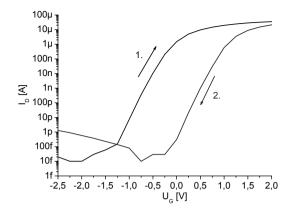

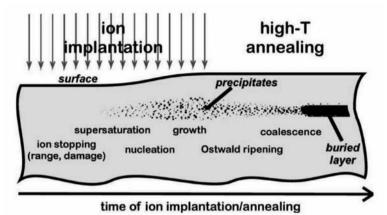

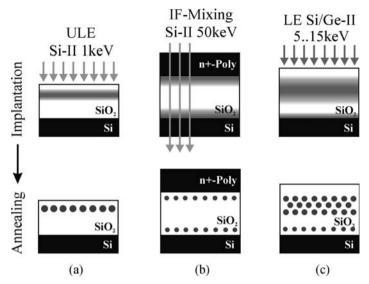

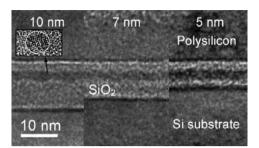

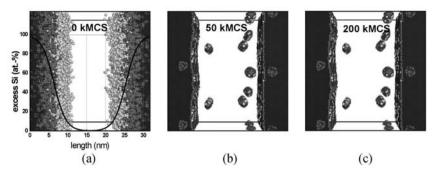

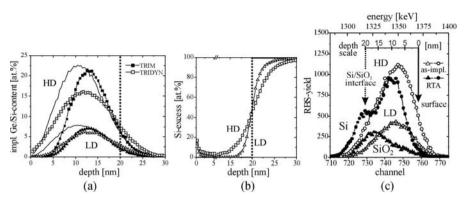

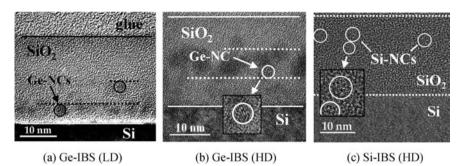

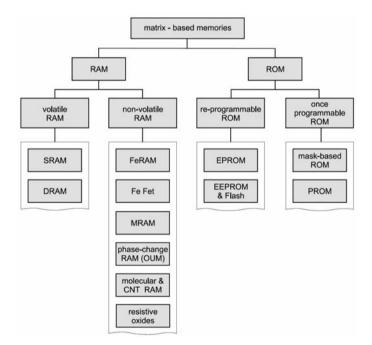

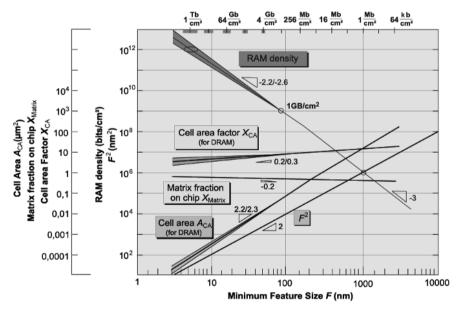

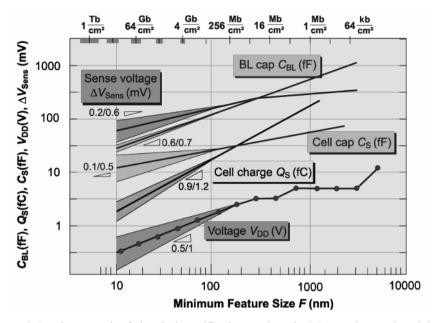

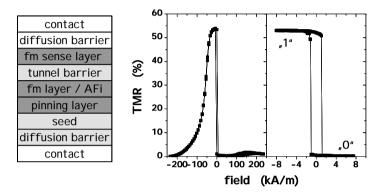

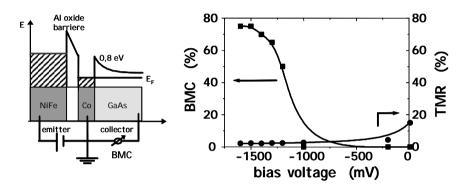

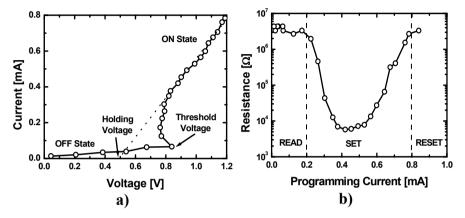

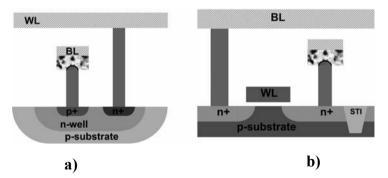

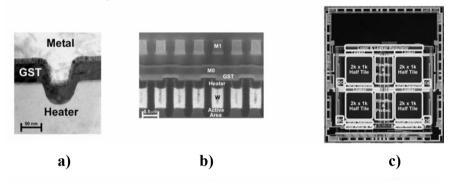

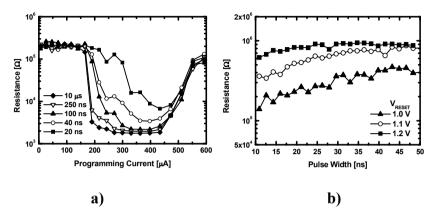

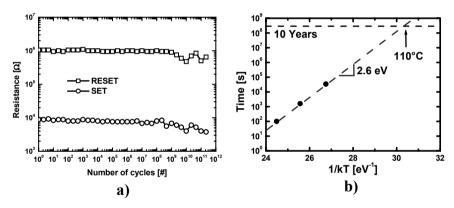

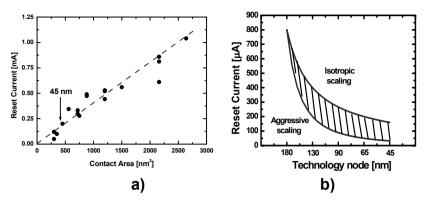

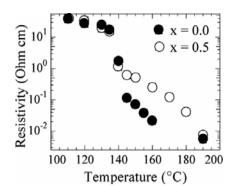

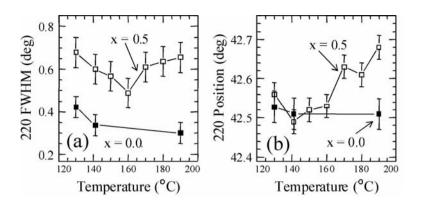

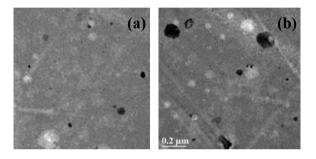

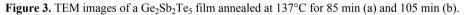

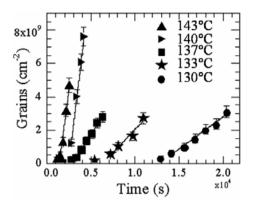

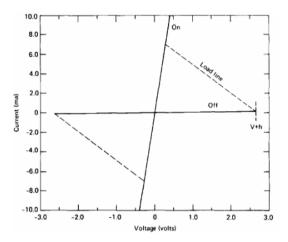

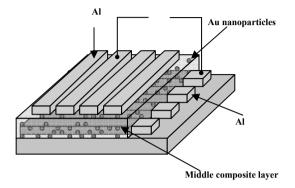

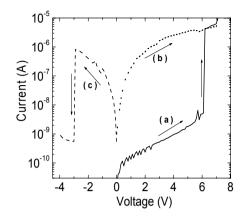

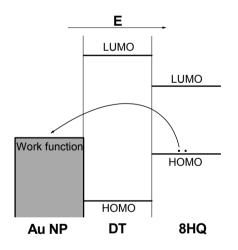

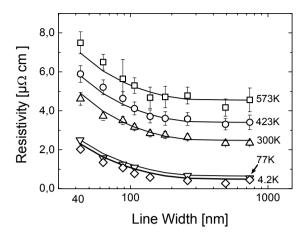

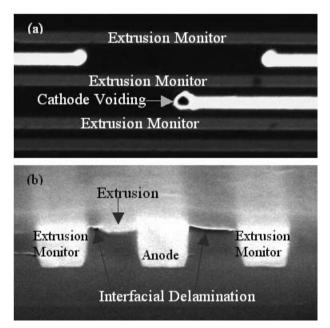

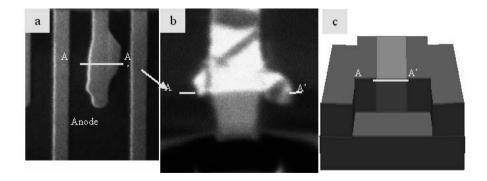

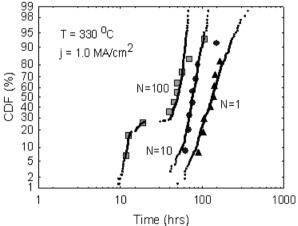

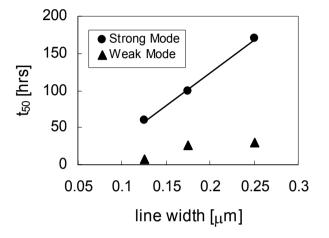

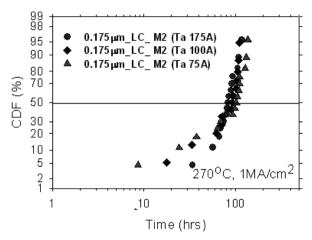

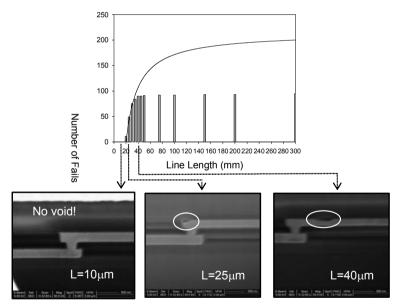

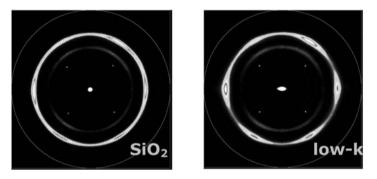

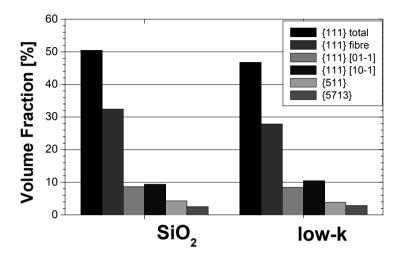

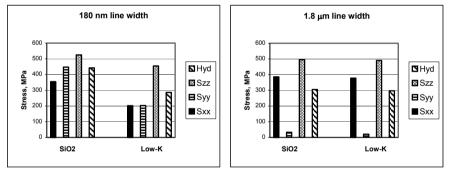

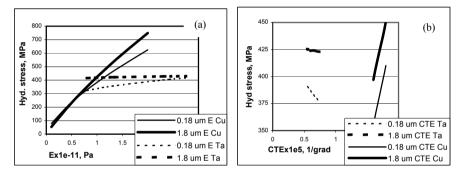

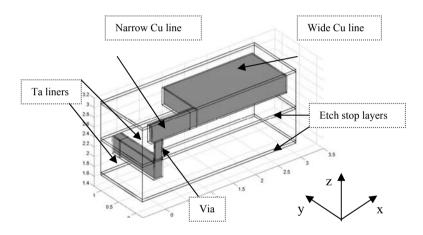

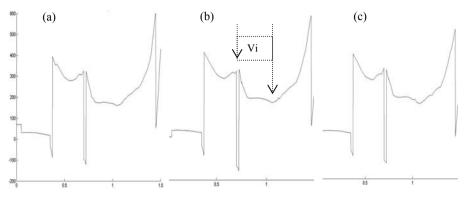

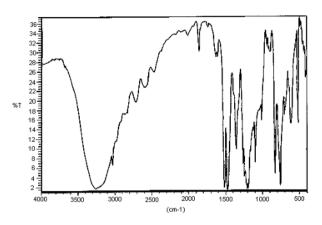

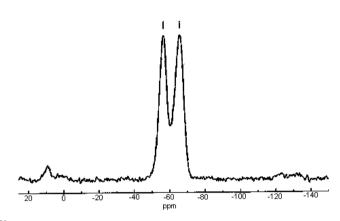

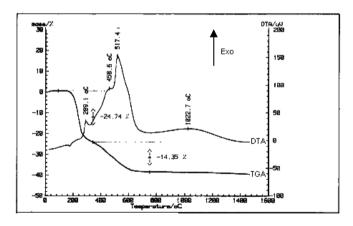

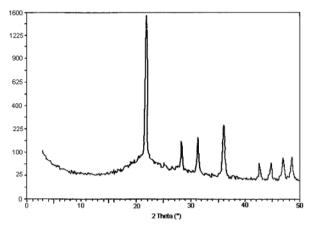

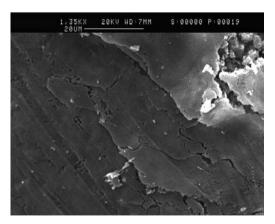

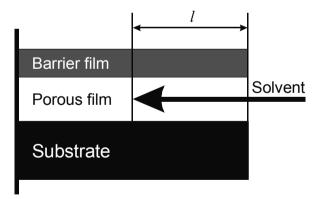

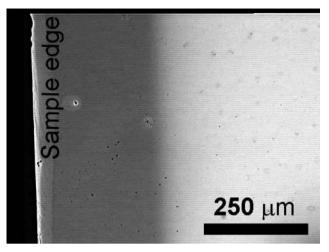

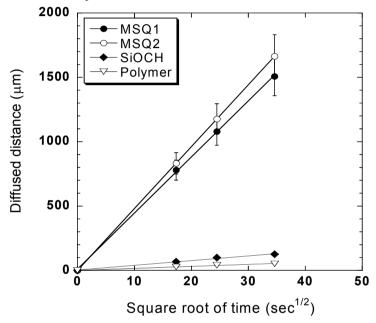

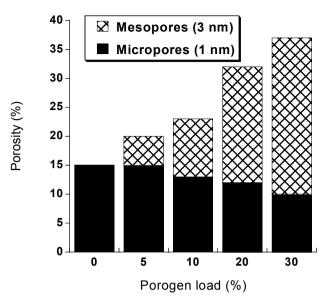

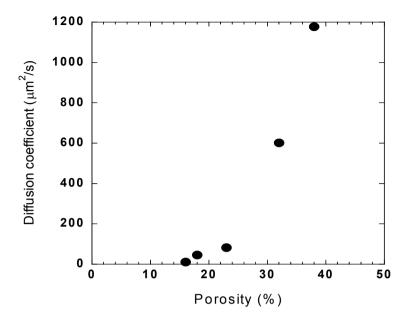

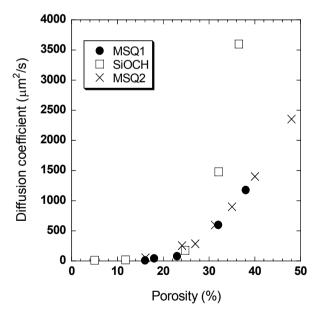

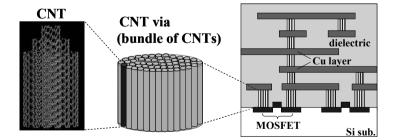

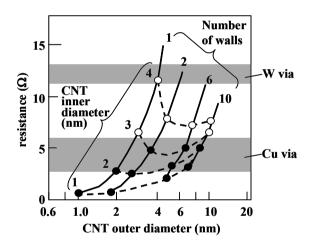

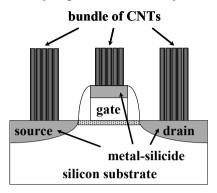

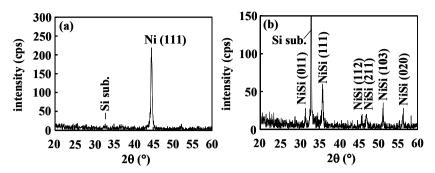

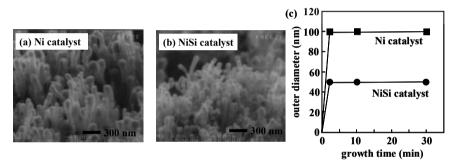

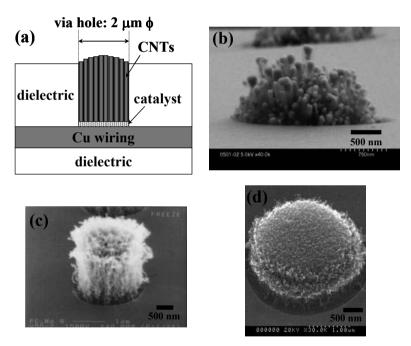

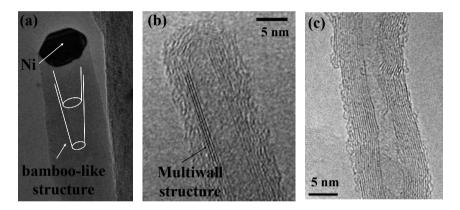

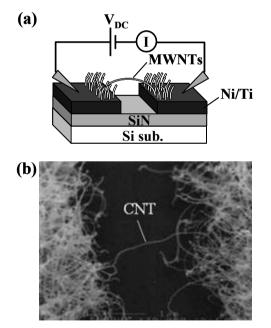

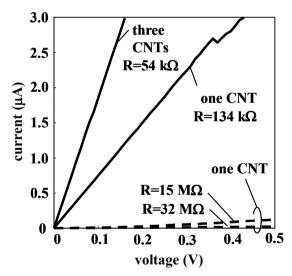

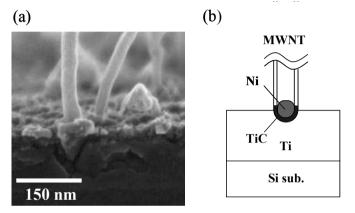

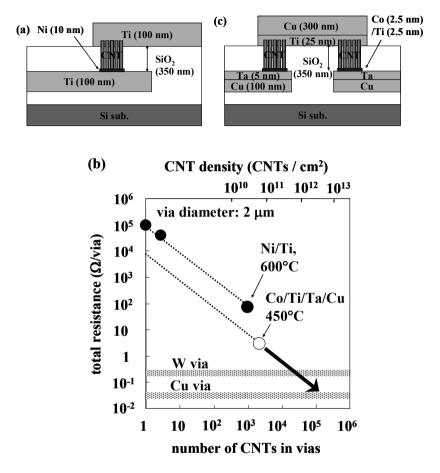

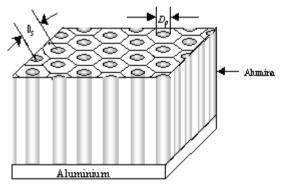

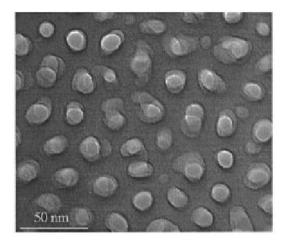

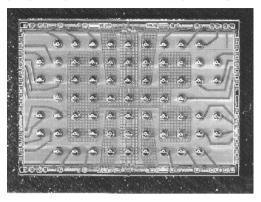

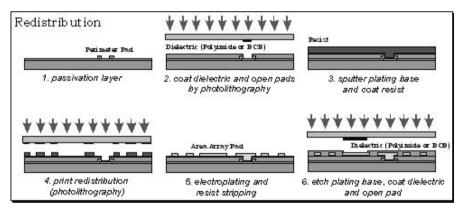

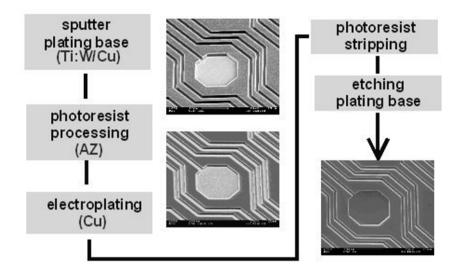

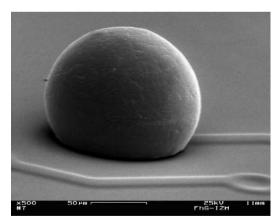

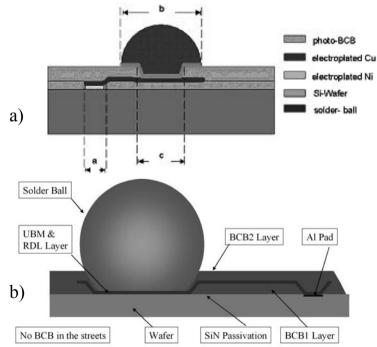

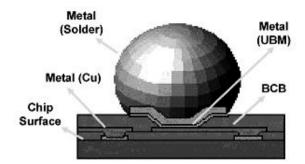

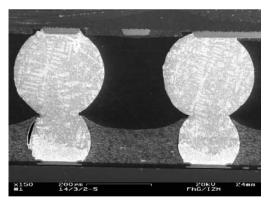

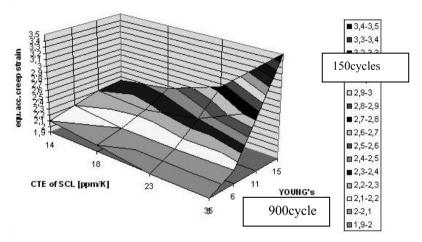

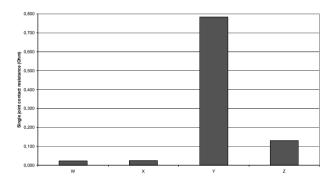

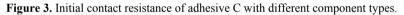

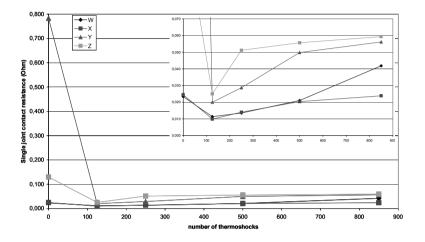

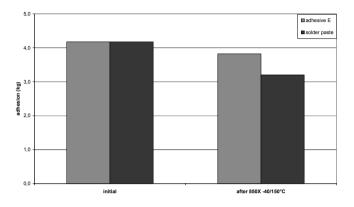

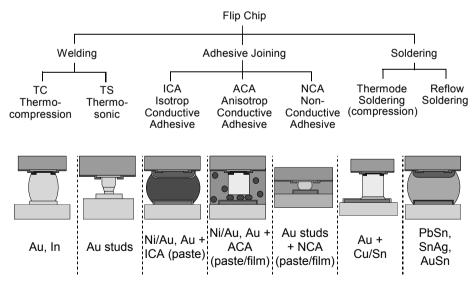

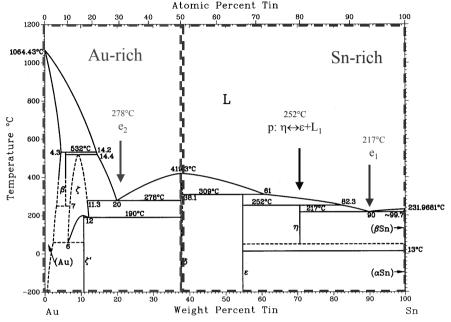

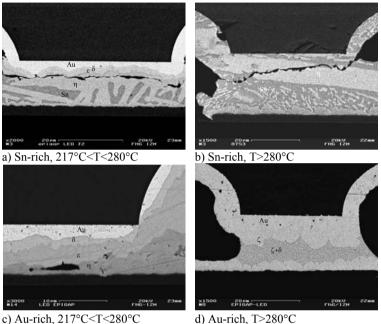

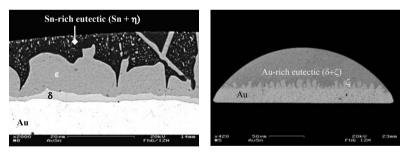

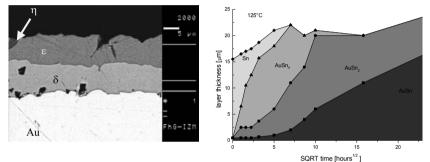

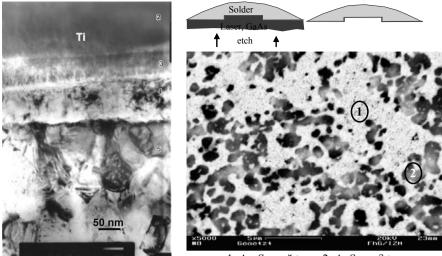

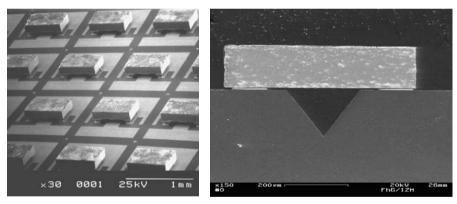

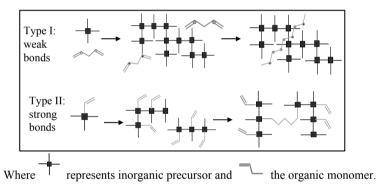

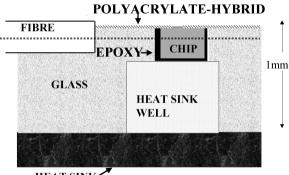

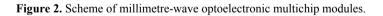

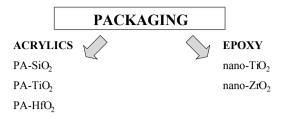

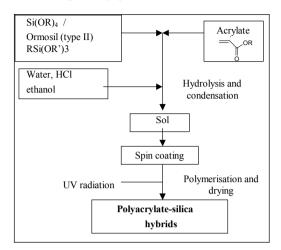

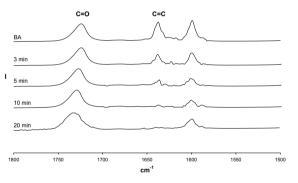

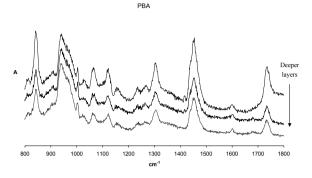

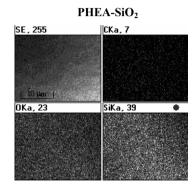

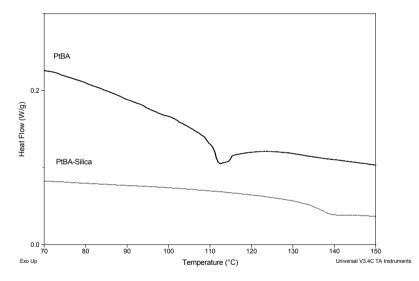

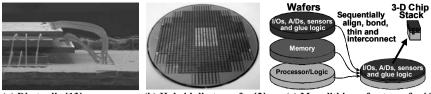

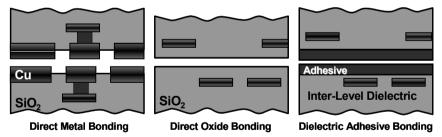

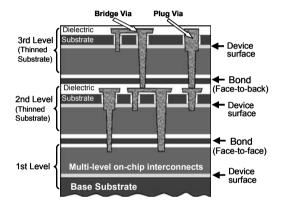

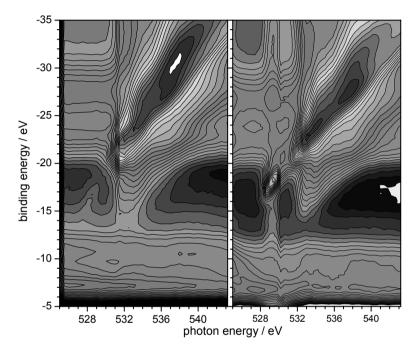

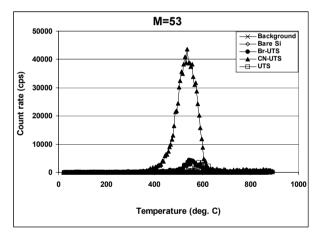

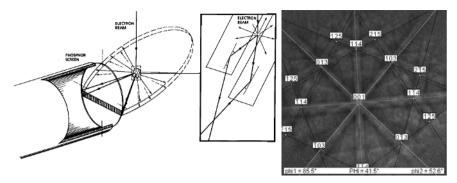

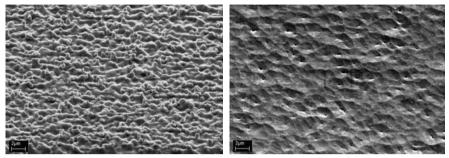

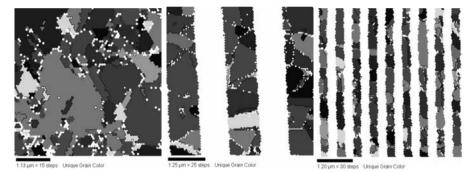

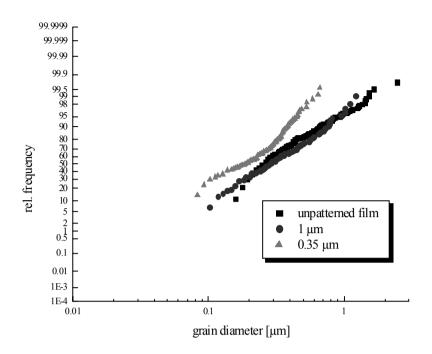

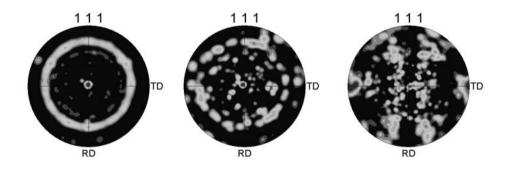

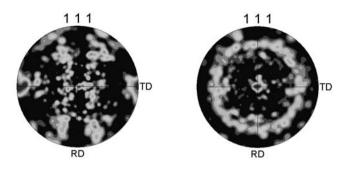

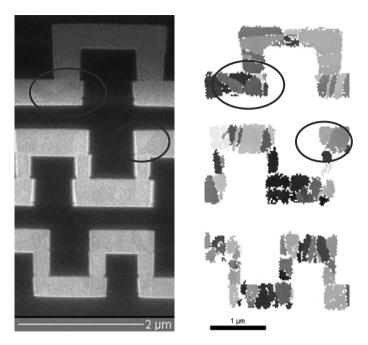

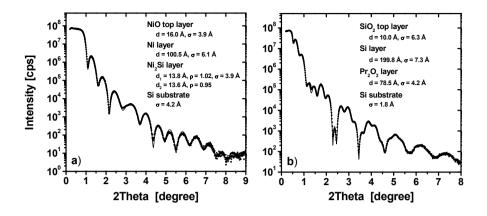

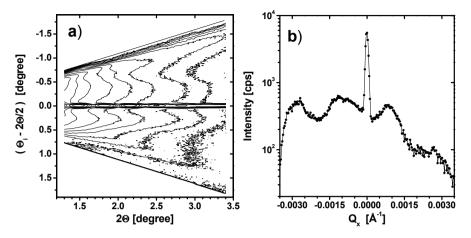

- D. Buca, B. Holländer, H. Trinkaus, S. Mantl, R. Carius, R. Loo, et al. Appl. Phys. Lett. 85, 2499 (2004)